Vorwort

Mit der schnellen Entwicklung von Kommunikation und elektronischen Produkten, Das Design von gedruckten Leiterplatten (Leiterplatten) Als Trägersubstrate bewegt sich zu höheren Ebenen und dichteren Konfigurationen. Rechnungswechsel oder Motherboards mit hohen Schichten mit dickeren Brettern, kleinere Löcher, und dichtere Routing wird eine erhöhte Nachfrage vor dem Hintergrund kontinuierlicher technologischer Fortschritte in der Informationstechnologie erzeugen, PCB-bezogene Herstellungsprozesse vorstellen.

Innovation im Elektroplattenprozess für HDI-Boards mit hohem Aspekt-Verhältnis.

Aufgrund des hohen Aspektverhältnisses der Durchgangslöcher (HARTs) in System-HDI-Karten, Der Beschichtungsprozess muss sowohl der HART-Verarbeitung genügen als auch gute Ergebnisse bei der Beschichtung von Sacklöchern liefern, Dies stellt eine Herausforderung für herkömmliche Gleichstrom-Galvanisierungsverfahren dar. Die widersprüchlichen Anforderungen von Harts und Blindlöchern stellen die größte Schwierigkeit bei der Überbearbeitung von Prozessen dar.

Grundsätze Einführung

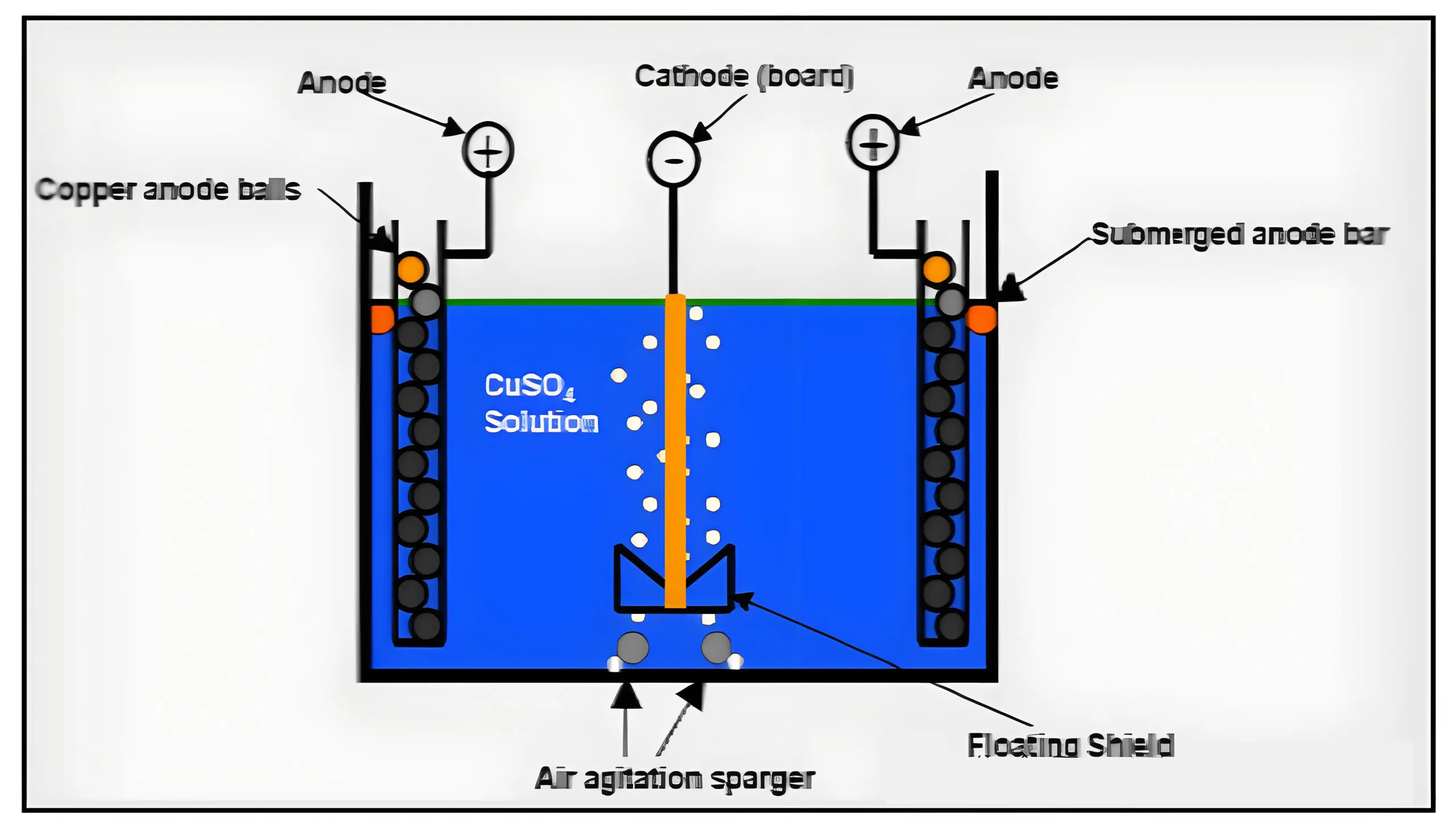

Prinzip der PCB -Platte

Lösungszusammensetzung und Funktion

— COSO4

Liefert die notwendige Cu2+ für die Überbeziehung, Erleichterung der Kupferionenübertragung zwischen Anode und Kathode.

— H2SO4

Verbessert die Leitfähigkeit der Plattierungslösung.

— Cl–

Hilft bei der Bildung des anodischen Films und der Auflösung der Anode, Verbesserung der Kupferablagerung und Kristallisation.

— Additive Plattierstoffe

Verbessern.

A. Das Konzentrationsverhältnis von Kupferionen zu Schwefelsäure und Salzsäure in der Kupfersulfat-Plattierungslösung beeinflusst direkt die tiefe Überbeamte von Durchlöchern und Blindlöchern.

B. Higher Kupferionengehalt führt zu einer schlechteren Leitfähigkeit der Lösungen, d.h., höherer Widerstand, Dies ist nachteilig auf einheitliche Stromverteilung. daher, Für Harts, ein niedriger Koper, Hochsäurehaltiges Lösungssystem ist erforderlich.

C. für blinde Löcher, aufgrund eines schlechteren Lösungskreislaufs innerhalb, Eine höhere Konzentration von Kupferionen ist erforderlich, um die Reaktion aufrechtzuerhalten.

Daher, Produkte, die sowohl Harts als auch Blindlöcher enthalten, die Schwierigkeit davon darstellen.

III. Experimentelle Konstruktions- und Ergebnisanalyse

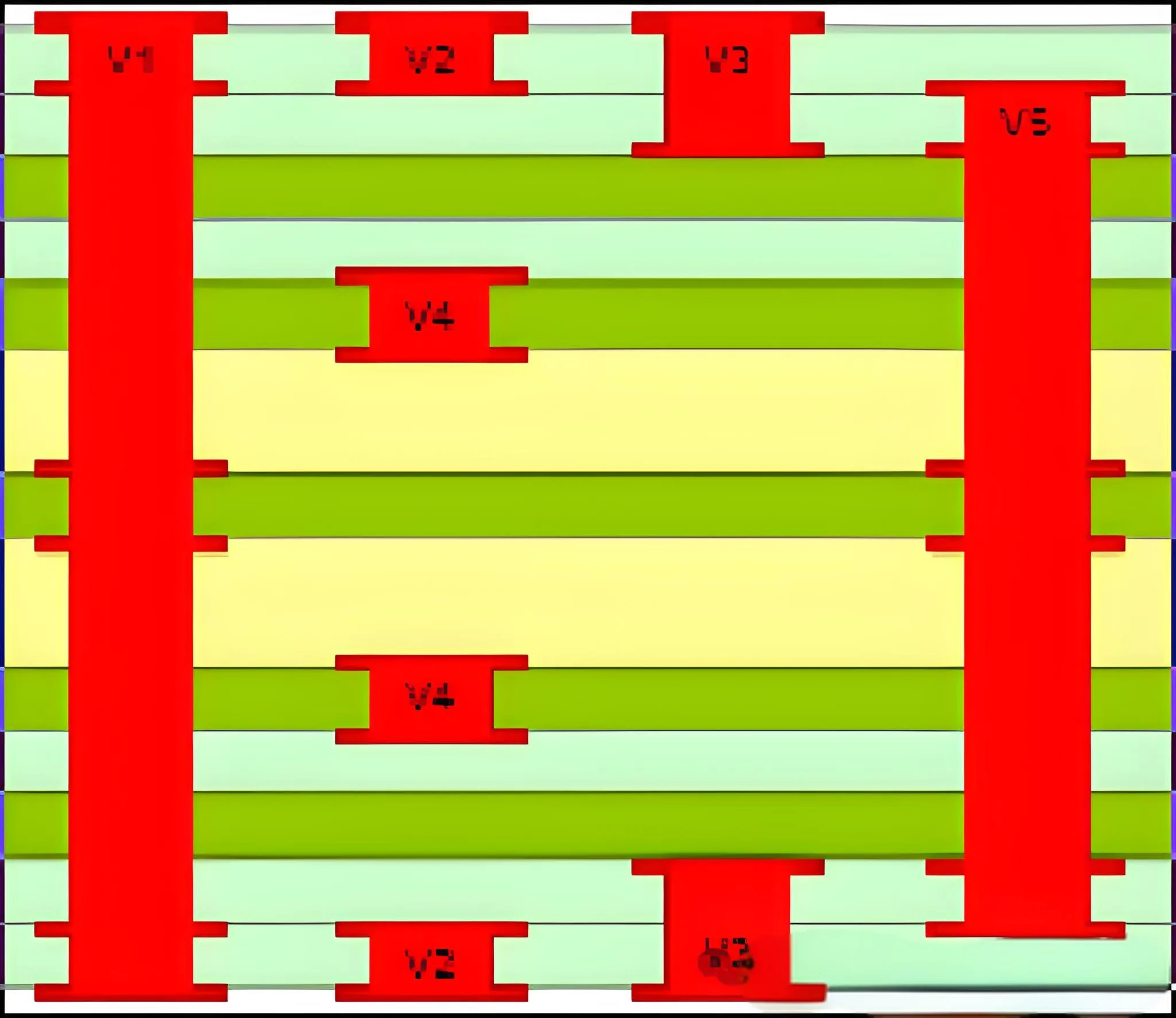

① Produktinformationen

Brettdicke: 2.6mm, Mindestdurchmesser durch den Durchmesser: 0.25mm,

Maximales Verhältnis von Durchlöchern: 10.4:1;

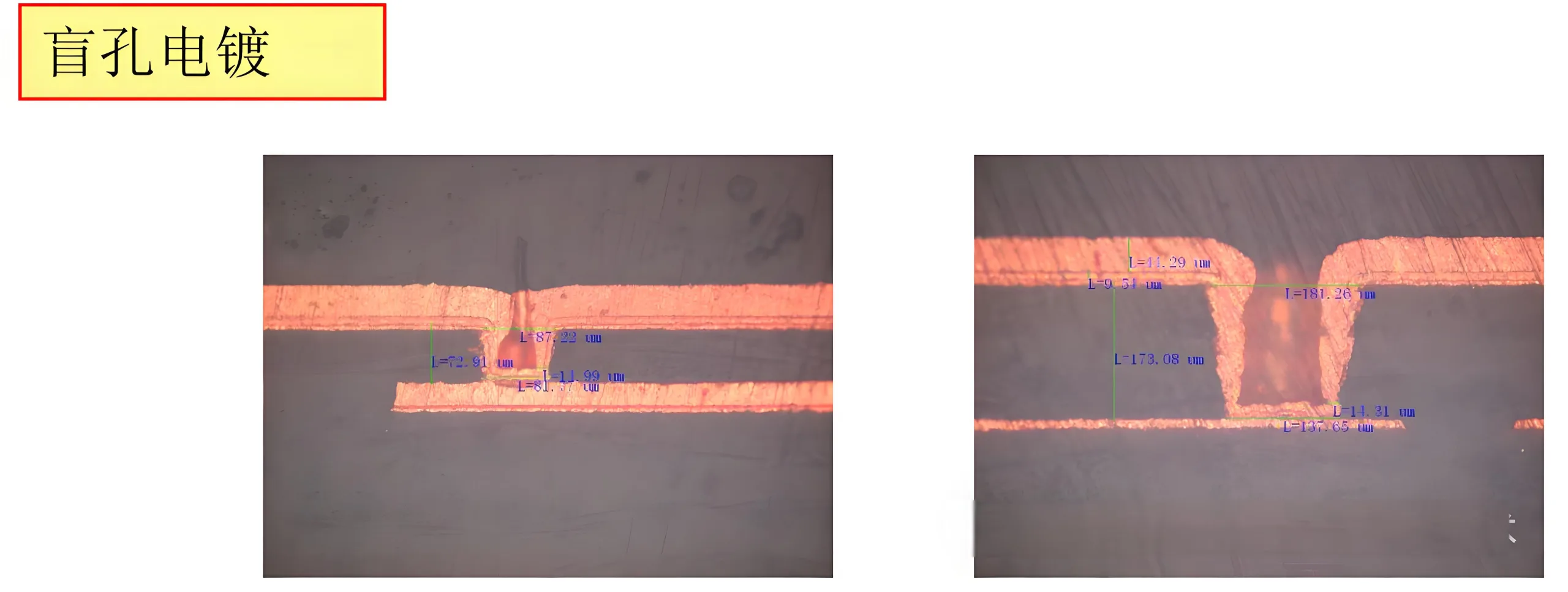

② Blindlöcher

1) Dielektrizitätsdicke 70um (1080pp), Lochdurchmesser 0,1 mm

2) Dielektrizitätsdicke 140um (2*1080pp), Lochdurchmesser 0,2 mm

Analyse der HDI -Plattierung experimentelle Ergebnisse basierend auf dem Seitenverhältnis

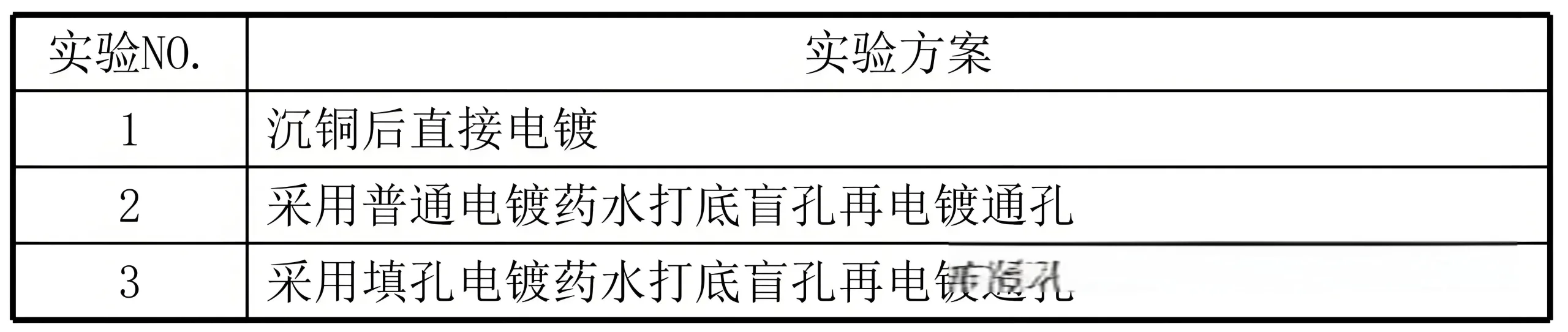

③ Parametereinstellungspläne

HDI -Elektroplatten experimenteller Plan

Plan eins

Direkte Beschichtung nach Kupferablagerung

Verwenden Sie eine hohe Säure, Lösungslösungsverhältnis mit H-Plattieradditiven; Aktuelle Dichte 10Asf, Plattierungszeit 180 Minuten.

Direkte Beschichtung nach Kupferablagerung

HDI Blind Lochbeschichtung

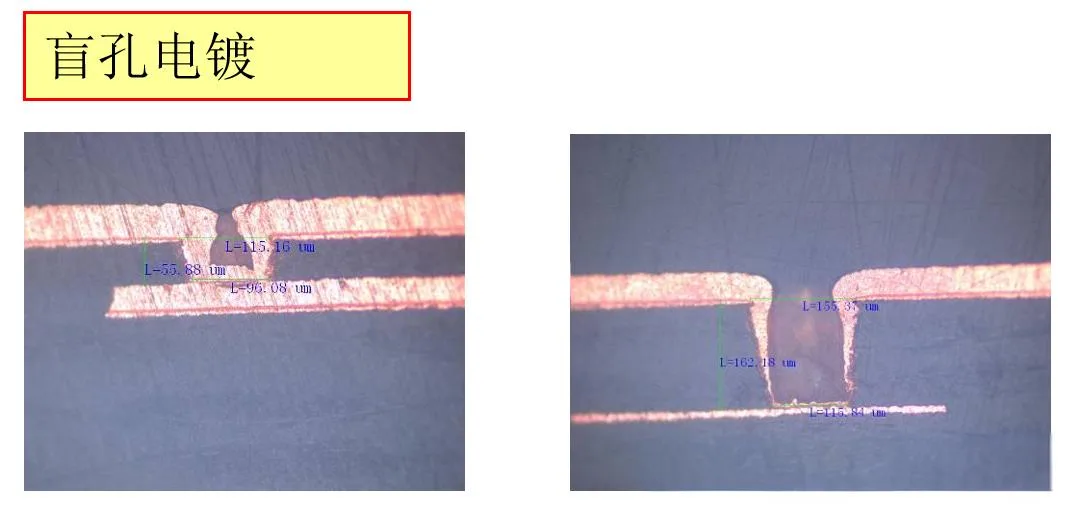

1) Dielektrizitätsdicke 70um (1080pp), Lochdurchmesser 0,1 mm: Locheingang versiegelt, Lochboden Kupferdicke 14-16um

2) Dielektrizitätsdicke 140um (2*1080pp), Lochdurchmesser 0,2 mm: Loch Bottom Crabgefeet, Dicke 4-5um

— Endgültige offene/kurze Testergebnisse

Diese Charge hatte eine 100% Ausfallrate im endgültigen offenen/kurzen Test, mit a 70% Ausfallrate speziell an der Position von 0,2 mm Blind Loch (Pp 1080*2).

Plan zwei

Testen Sie die Standardbeschichtungslösung für Blindlöcher, gefolgt von der Durchlögelbeschichtung:

1) Verwenden Sie VCP für die Basis -Blind -Loch -Platte, Standard-Säure-Kupper-Verhältnis, H Plattieradditive, Aktuelle Dichte 15asf, Plattierungszeit 30 Minuten

2) Verwenden Sie eine Drachenlinie zur Verdickung, hochsäurehaltig, Additive mit niedriger Koper und H-Plattierung, Aktuelle Dichte 10Asf, Plattierungszeit 150 Minuten

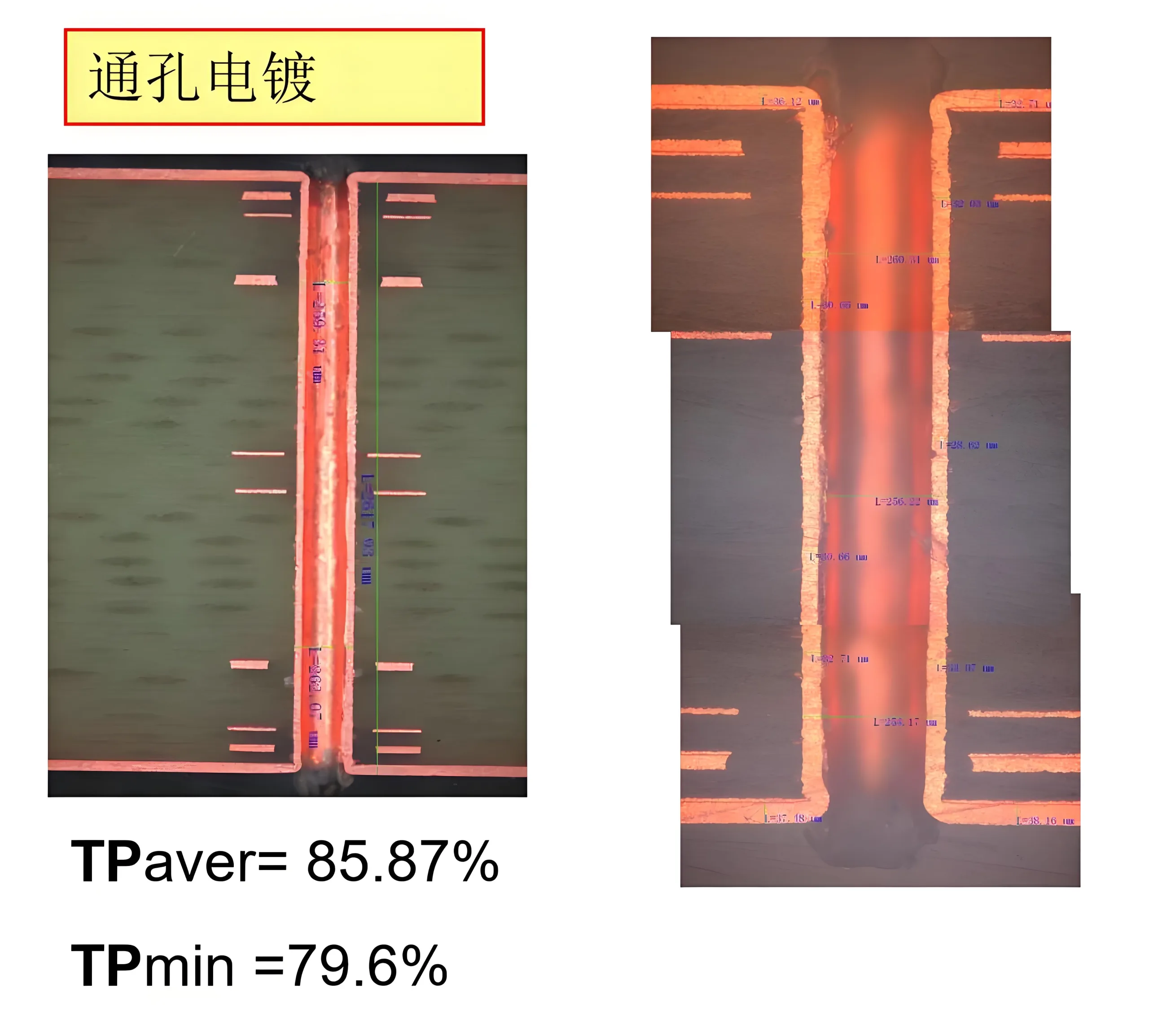

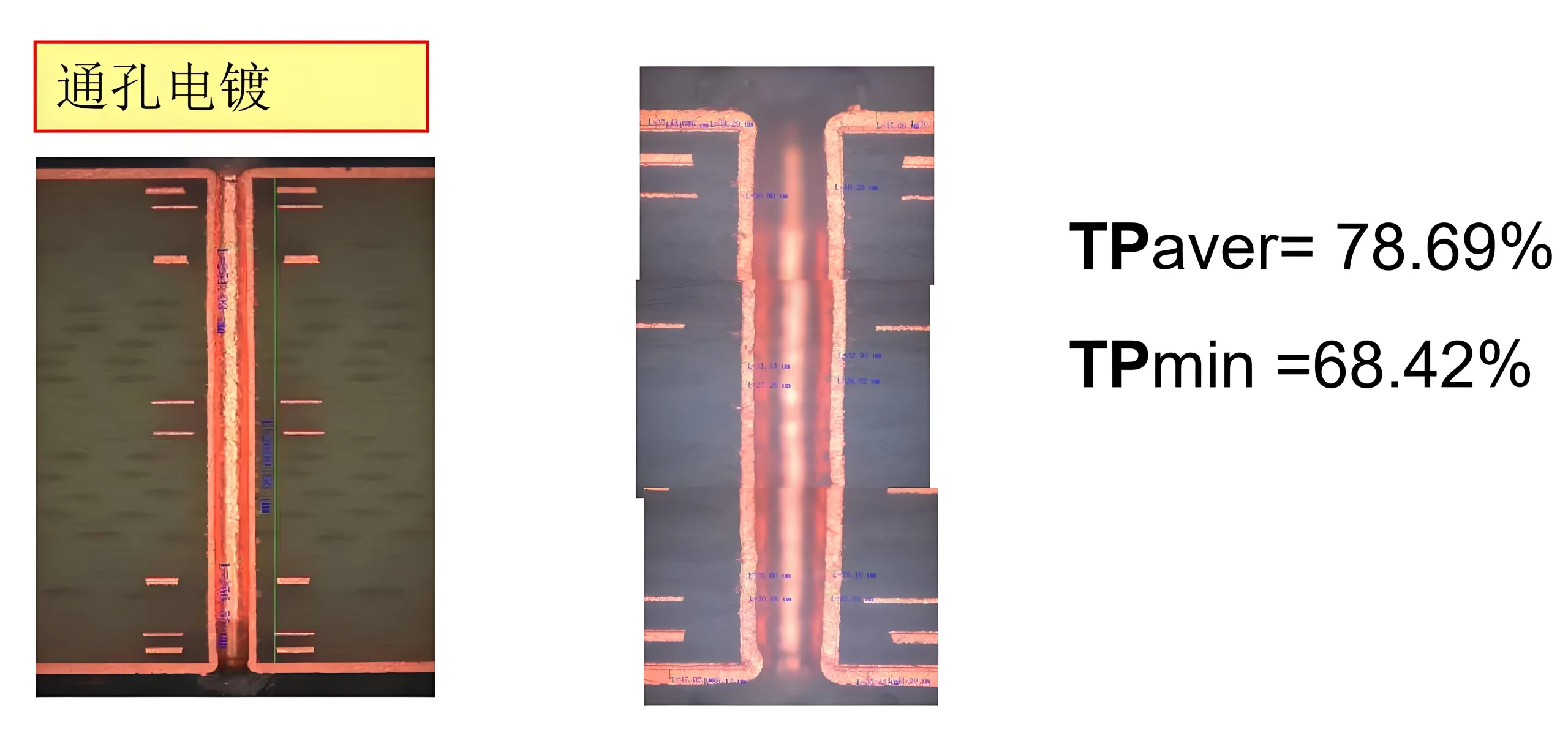

HDI-DurchlöCHE-Plattierung

HDI Blind Lochbeschichtung

1) Dielektrizitätsdicke 70um (1080pp), Lochdurchmesser 0,1 mm: Locheingang versiegelt, Lochboden Kupferdicke 14-16um

2) Dielektrizitätsdicke 140um (2*1080pp), Lochdurchmesser 0,2 mm: Loch Bottom Crabgefeet, Dicke 14-16um

— Endgültige offene/kurze Testergebnisse

Diese Charge hatte eine 45% Ausfallrate im endgültigen offenen/kurzen Test, mit a 60% Ausfallrate speziell an der Position von 0,2 mm Blind Loch (Pp 1080*2).

Vergleich der beiden Experimente, Das Hauptproblem lag mit dem Blindloch -Plattieren, validieren, dass die hohe Säure, System mit niedrigem Kupferlösungssystem ist für blinde Löcher ungeeignet.

daher, in Experiment drei, Wir haben uns für eine Säure ausgewählt, Hochcopper-Fülllochlösung für die Basisblindlochbeschichtung, Füllen Sie den Boden der blinden Löcher, bevor Sie mit einer blinden Lochbeschichtung fortfahren.

Plan drei

Verwenden der Fülllochbeschichtungslösung für die Basis-Blindloch-Plattierung, gefolgt von der Durchlögelbeschichtung:

1) Verwenden Sie Fülllochbeschichtungslösung für die Basisblindlochbeschichtung, Hochkoper-Kupferverhältnis mit niedrigem Säure und V-Plating-Additive, Plattierungsparameter 8asf@30min+12@ASF30Min

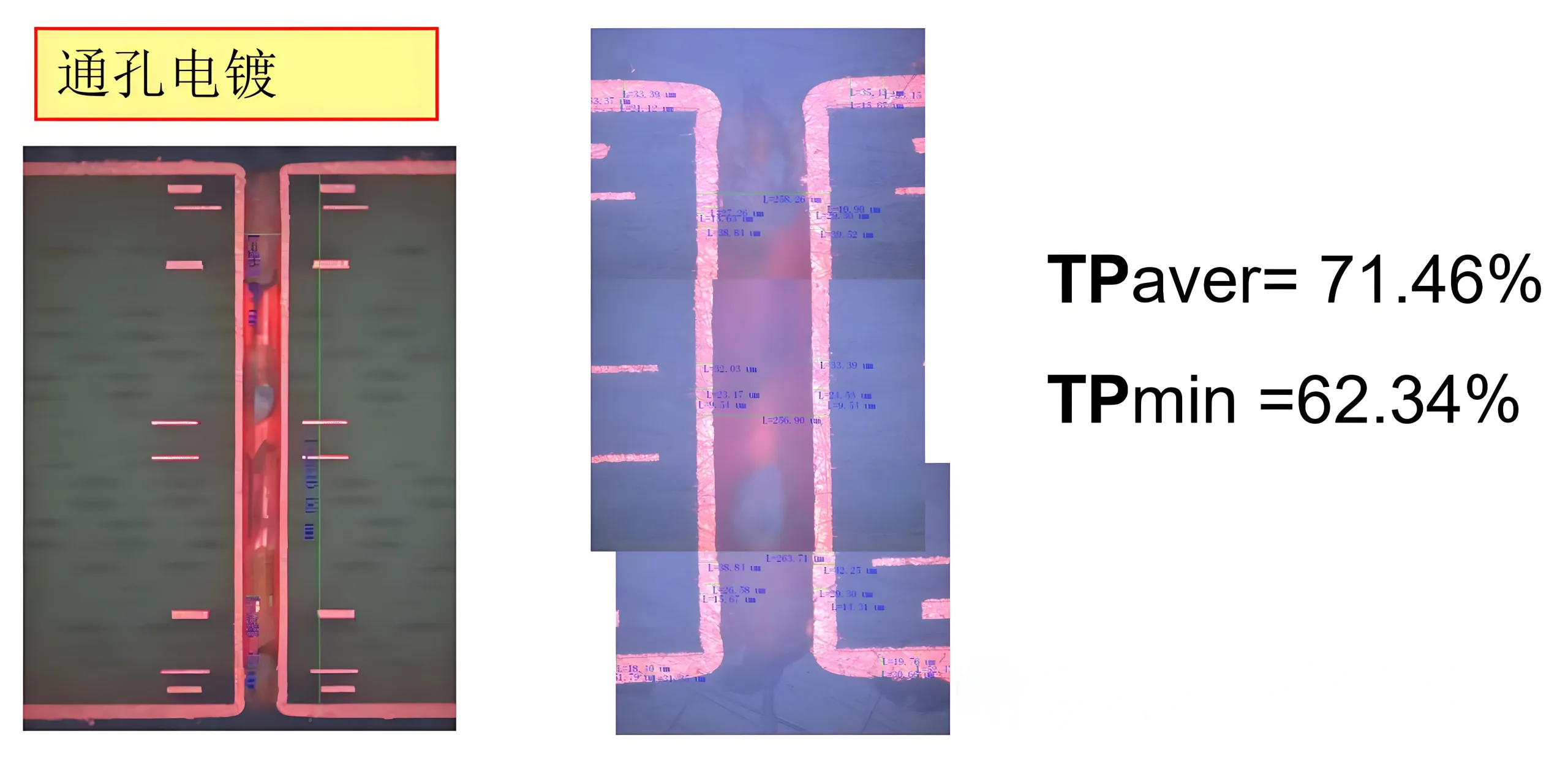

2) Verwenden Sie eine Drachenlinie zur Verdickung, Hochsäurehalte und H-Plattieradditive mit niedrigem Koper-Verhältnis, Plattierungsparameter 10Asf, Plattierungszeit 150 Minuten

Überladung durch das Lochvias mit einer leitenden Basis vor der Elektrierung

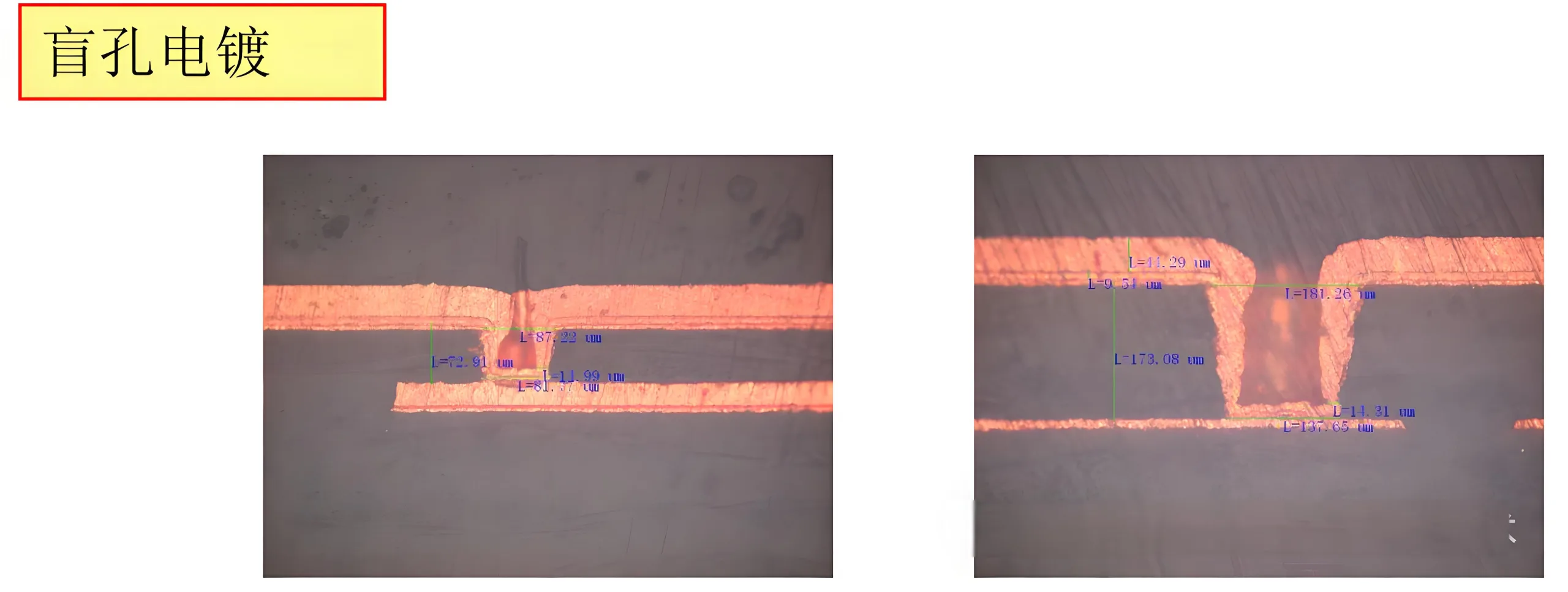

HDI Blind Lochbeschichtung

1) Dielektrizitätsdicke 70um (1080pp), Lochdurchmesser 0,1 mm: Blindes Loch gefüllt

2) Dielektrizitätsdicke 140um (2*1080pp), Lochdurchmesser 0,2 mm: Blindlochdicke 73,63um

Experimentelle Konstruktions- und Ergebnisanalyse

Durch experimentellen Vergleich, Verschiedene Verhältnisse der Säure-Kupper und Plattieradditive zeigen unterschiedliche Auswirkungen auf und blinde Lochbeschichtung. Für HDI -Board, Es ist notwendig, einen Gleichgewichtspunkt zu finden, um Probleme mit Kupferdicke durch Löcher und Krabben in Blindlöchern zu beheben. Eine solche verarbeitete Oberflächenkupferdicke ist tendenziell dicker, Oft erfordert sich mechanisches Bürsten.

In den endgültigen Kupfer Break -Tests, Alle drei Chargen zeigten Verbesserungen, mit dem ersten und zweiten Chargen mit 100% Und 45% Ausfallraten, vor allem an der 0,2 -mm -Stelle des Blindlochs (Pp 1080*2) mit Ausfallraten von 70% Und 60%, während die dritte Charge ohne solche Probleme vollständig verging, Erreichen a 100% Passquote und signifikante Verbesserung nachweisen.

Schließende Bemerkungen

Diese Verbesserung bietet eine effektive Lösung für den Elektroplattenprozess von HDI -Boards mit hohem Seitenverhältnis, Die Optimierung der Parameter ist jedoch noch erforderlich, um eine dünnere Kupferdicke der Oberfläche zu erreichen. Es ist zu hoffen, dass dies als wertvolle Referenz für Gleichaltrige dienen kann, Angebot verkürzter und überschaubarer Verarbeitungsverfahren für die Herstellung von HDI -Board -Board -Verhältnissen mit hohem Seitenverhältnis.

UGPCB-LOGO

UGPCB-LOGO