Die Technik, einzelne Einheiten aus Wafern zu schneiden und sie dann zu verpacken. Jedoch, Dieser Ansatz wird derzeit nicht von großen Halbleiterherstellern aufgrund hoher Herstellungskosten und der zunehmenden HF -Komponente der heutigen Module übernommen. Daher, das Aufkommen der Verpackung auf Waferebene (WLP) hat zu einer Paradigmenverschiebung bei der Entwicklung von kostengünstigen Verpackungen geführt. WLP ist eine Wafer -Level -Verpackungstechnologie vor dem Abschneiden von Waferverpackungsgeräten.

Verwenden von Standardwerkzeugen und -prozessen, WLP fungiert als Erweiterung des Waferherstellungsprozesses. Letztlich, Der hergestellte WLP -Würfel hat ein metallisiertes Pad auf der Oberfläche des Chips und einen Lötmittelpunkt, der vor dem Schneiden des Wafers auf jedem Pad abgelagert wird. Das, wiederum, macht WLP kompatibel mit herkömmlichen PCB -Montageprozessen und ermöglicht Geräte -Tests auf dem Wafer selbst. Infolge, Es ist ein relativ kostengünstiger und effizienter Prozess, Vor allem, wenn die Wafergröße zunimmt und der Chip stirbt, schrumpft. Die Größe der Wafer hat in den letzten Jahrzehnten zugenommen, aus 4, 6, Und 8 Zoll im Durchmesser bis 12 Zoll. Dies führt zu einer Erhöhung der Anzahl der Stanzteile pro Wafer, was die Produktionskosten senkt. In Bezug auf die elektrische Leistung, WLP ist anderen Verpackungstechnologien überlegen, In dem Sinne, dass sobald ein WLP -Gerät in ein dichter HF -Modul integriert ist, Dies führt zu einer signifikanten Verringerung der parasitären EM -Kopplung, da die Verbindung zwischen dem Gerät und der PCB relativ kurz ist, Im Gegensatz zur drahtgebundenen Verbindung, die in einigen Arten von CSP-Technologien verwendet wird.

WLP-Chip-Flip-Chip-Technologie

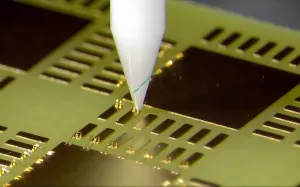

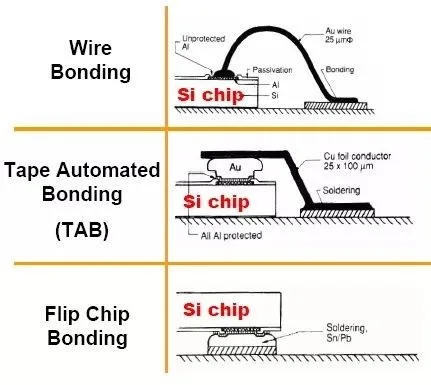

Flip-Chip-Technologie, Auch als die kontrollierte Zusammenbruchchip -Verbindung bezeichnet (C4), ist eine von mehreren Chip -Assembly -Technologien, die in den 1960er Jahren von IBM entwickelt wurden. Obwohl die Verpackungstechnologie auf der Bindung auf Drahtbindungen in Bezug auf die freie induktive Fähigkeit zum Debuggen der Labor nach dem Erstellen der Hardware flexibler ist, und bietet auch eine gute thermische Leitfähigkeit, Die Verwendung von Lötbulden in der Flip-Chip-Verpackungstechnologie macht die elektrische Verbindung zwischen dem Paketsubstrat und dem ChIP relative Größenreduzierung liefert, Reduzierte Latenz, und bessere Isolation in Bezug auf die Eingangs- und Ausgangsstifte. Figur 1 zeigt die Grundstruktur des Chip -Würfels auf dem Substrat, mit einem Lötball oben in der Cu -Säule wächst auf der Chipoberfläche. Die Lötverbindung wird normalerweise mit einer Füllstoffformmasse eingekapselt, um die Lötverbindung mechanisch zu unterstützen.

WLP-Chip-Flip-Chip-Technologie

WLP Chip Level -Paket

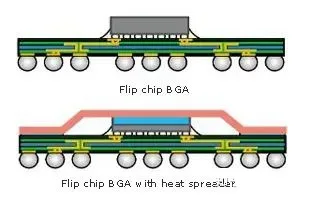

Chip -Skala -Verpackung (CSP) ist eine der am häufigsten verwendeten Verpackungsmethoden in der Mikroelektronik- und Halbleiterindustrie. Während Mikrochip -Hersteller bereits verschiedene Arten von CSP -Technologien zur Verfügung stehen, Neue Typen entstehen weiterhin, um die Nachfrage nach Produkten zu decken, die neue Funktionen und neue anwendungsspezifische Produkte unterstützen. Diese Verpackungsanforderungen können je nach dem erforderlichen Zuverlässigkeitsniveau variieren, kosten, Zusätzliche Funktionen, und Gesamtgröße. Wie der Name schon sagt, Die Packungsgröße des CSP ist ungefähr die gleiche wie die Chip -Sterbegröße, Das ist einer seiner Hauptvorteile. Durch Übernahme des WLP -Herstellungsprozesses, CSP wird ständig entwickelt, um das kleinstmögliche Verhältnis von Paket-Die-Größen zu erreichen. Wie in Abbildung gezeigt 2, das Ballgitterarray (BGA) Der CSP -Stil im Paket ermöglicht mehrere Verbindungen bei der Vereinfachung der PCB -Verkabelung, Erhöhung der Durchsatz von PCB -Baugruppen und Reduzierung der Fertigungskosten.

Waferspiegelverpackung

Andere Einkapselungstechnologien

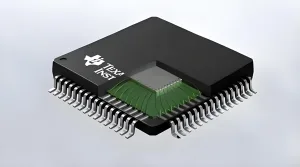

Es gibt mehrere andere Formen integrierter IC-Verpackungen, die eine nahtlose Integration in Anwendungsmodulpakete ermöglichen. Quad -Flat -Paket (MFR) ist eine der frühesten oberflächenbergigen IC-Paket-Technologien,wobei die Struktur des Pakets aus vier Seiten mit erweiterten Verbindungsleitungen besteht, Wie in Abbildung gezeigt 3(A). Die erhöhten Leitungen sind mit dem Packungsrahmen angeschlossen, um eine Metall-INSERLOSLLEL-Metal zu bilden (Mim) Typkondensator zwischen den Leitungen und dem Chip -Die -Metall, die als passendes Element verwendet werden können. Diese Technik eignet sich für ICs in Millimetergröße 100 Stifte. Es gibt mehrere Derivate dieser Art von Kapselung, Abhängig vom verwendeten Material, wie Keramikquad Flat Pack, Dünne Quad -Flachpack, Plastikquad Flachpackung, Plastikquad Flachpackung) und Metall Quad Flat Pack (MQFP). Das QFN, Quad flach ohne Blei, in Abb. 3(B) ist eine von mehreren an Oberflächen montierten Verpackungstechnologien, die aus einem flachen Kupfer-Bleirahmen gebildet wurden, und ein Kunststoffpaket, das als Wärmeübertragungskissen für den Kühler verwendet wird. Drahtbindung kann auch für Vernetzung verwendet werden, und da Bindungslinien nicht nur Leiter, sondern auch Induktoren sind, Sie beeinflussen im Allgemeinen die Leistung von Geräten im Rahmen dieser Kapselungstechnik, es sei denn, es wird als Teil des Gesamtdesigns betrachtet. Obwohl das QFN eine Verbindung ist, die aus vier Seiten besteht, Die ungeleiteten Bi-Ebenen-Leads (DFN) haben auch beide Seiten der Interconnect -Ebene -Leads erschienen und bildeten.

UGPCB-LOGO

UGPCB-LOGO