emballage de puce

IC PCB & Conditionnement- Lorsque vous parlez de l'avenir de la technologie portable, Le futur cours de l'innovation technologique portable est clair. Il est fort et clair que pour réussir, L'électronique portable doit être petite et toujours effectuée. Cet article se concentre sur les exigences de la plaquette – puce de niveau – Emballage de niveau dans SRAM .

Pour réduire l'empreinte, et donc l'espace du conseil global, Les microcontrôleurs migrent vers des nœuds de processus plus petits toutes les autres génération. En même temps, Ils évoluent pour effectuer des opérations plus complexes et puissantes. À mesure que les opérations deviennent plus complexes, il y a un besoin urgent d'augmenter la mise en cache. Malheureusement, avec chaque nouveau nœud de processus, Ajout de cache intégré (sram intégré) devient difficile pour un certain nombre de raisons, y compris SER plus élevé, rendement inférieur, et une consommation d'énergie plus élevée. Les clients ont également des exigences SRAM personnalisées. Pour que les fabricants MCU fournissent toutes les tailles de cache possibles. Cela a motivé la nécessité de limiter le SRAM intégré sur le noyau du contrôleur et de le mettre en cache via un SRAM externe.

Cependant, Étant donné que la SRAM externe occupe une grande quantité d'espace de carte PCB, L'utilisation de SRAM externe fait face au défi de la miniaturisation. En raison de son architecture à six transistors, Réduire la taille du SRAM externe en portant le SRAM externe à un nœud de processus plus petit introduira les mêmes problèmes qui ont tourmenté le SRAM embarqué miniaturisé.

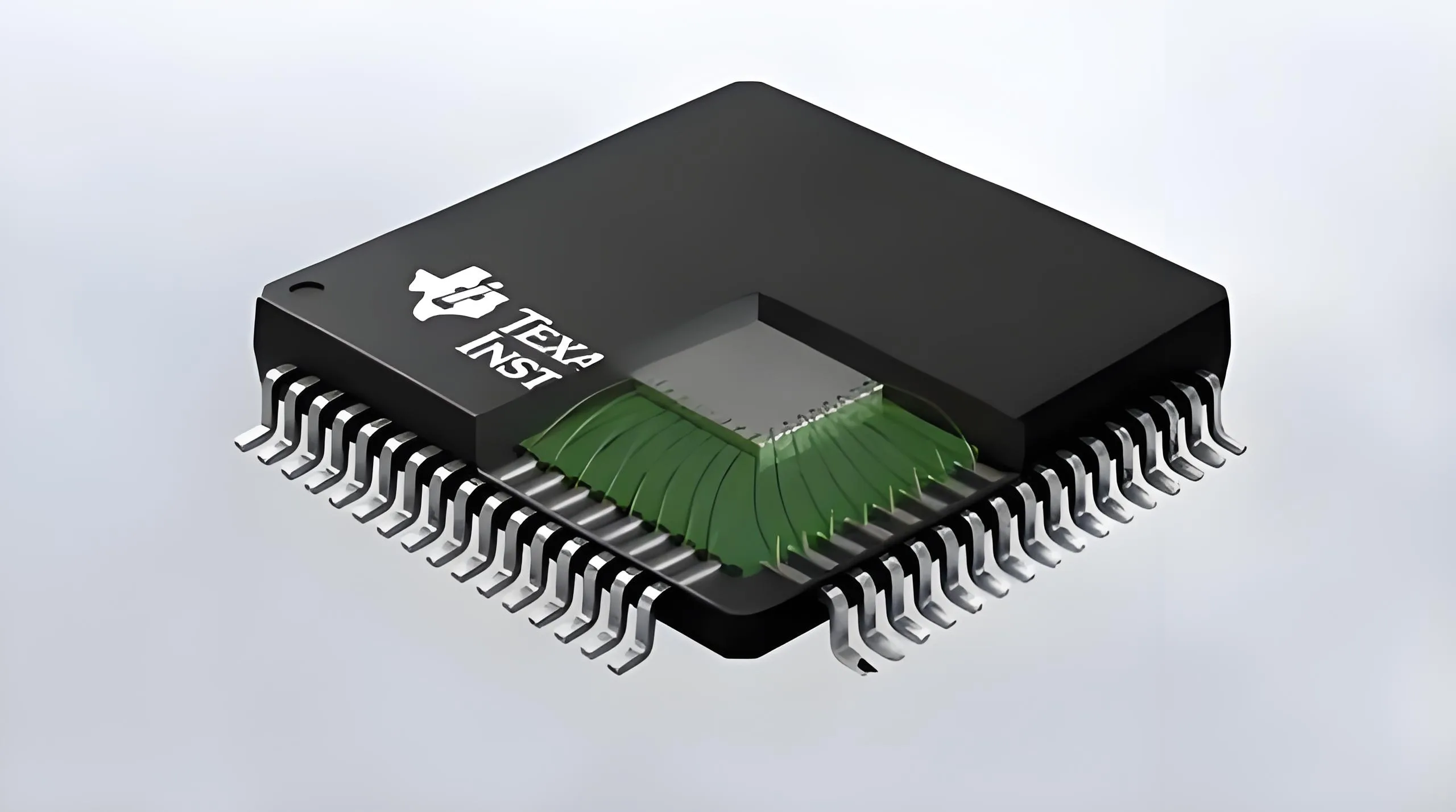

Cela nous amène à la prochaine alternative à ce problème séculaire: Réduire le rapport de l'emballage de puce à la taille de la puce dans le SRAM externe. Typiquement, Les puces SRAM emballées ont plusieurs fois la taille de la puce nue (jusqu'à 10 fois). Une solution courante à ce problème consiste à ne pas utiliser du tout des puces SRAM encapsulées. Il est logique de prendre une puce SRAM (1/10 taille) puis emballer avec une puce MCU en utilisant un emballage multi-chip complexe (MCP) ou technologie d'emballage 3D (également connu sous le nom d'emballage au niveau du système SIP). Mais cette approche nécessite des investissements importants et n'est faisable que pour les plus grands fabricants. Du point de vue de la conception, Cela réduit également la flexibilité car les composants de SIP ne sont pas facilement remplacés. Par exemple, Si la nouvelle technologie SRAM est disponible, Nous ne pouvons pas facilement remplacer la puce SRAM dans SIP. Pour remplacer l'une des puces nues dans le package, La gorgée entière doit être réauthentifiée. La requalification nécessite un réinvestissement et plus de temps.

Il y a donc un moyen d'économiser de l'espace de la planche tout en excluant le SRAM du MCU sans mettre le MCP en difficulté? Revenir au rapport noyau-puce-puce, Nous voyons de la place pour une amélioration significative. Pourquoi ne vérifiez-vous pas s'il y a un paquet qui s'adapte au moule? Autrement dit, Si vous ne pouvez pas déballer, Veuillez réduire l'échelle de taille.

Actuellement, l'approche la plus avancée consiste à réduire la taille du package de puces en utilisant WLCSP (Emballage de niveau de puce de niveau de plaquette). WLCSP fait référence à la technologie de couper les unités individuelles d'une plaquette en petits morceaux, puis de les assembler dans un paquet. L'appareil est essentiellement une puce nue avec un motif de dot ou de réseau sphérique surélevé qui ne nécessite aucune ligne de liaison ou connexion de couche intermédiaire. En fonction des spécifications, La zone d'un package au niveau des puces est à la hauteur 20% plus grand que celui de la puce. Le processus a maintenant atteint un niveau innovant où les usines de fabrication peuvent produire des composants CSP sans augmenter la zone des puces (Avec seulement une légère augmentation de l'épaisseur pour s'adapter à la bosse / sphère).

Nombres. Tranche – sur – emballage de puce (Wlcsp) Fournit la méthode la plus avancée pour réduire la taille de la nure emballée – ébrécher. Le WLCSP montré ici a été développé par Deca Technologies et n'augmente pas la zone des puces qui le composent. (Crédit: Deca Technologies / Cypress Semiconductor)

CSP a des avantages par rapport au film non enduit. Les appareils CSP sont plus faciles à tester, poignée, assembler, et réécrire. Ils ont également des propriétés de conductivité thermique améliorées. Lorsque le noyau est transféré vers des nœuds de processus plus récents, Il est possible de réduire le noyau tout en normalisant la taille CSP. Cela garantit que les composants CSP peuvent être remplacés par une nouvelle génération de composants CSP sans aucune complication associée à la modification du moule.

Évidemment, Ces économies d'espace sont importantes en termes de demande de portables et d'électronique portable. Par exemple, Le BGA à 48 balles utilisé dans la mémoire IC dans de nombreux appareils portables a aujourd'hui une taille de 8 mmx6mmx1mm (48MM3). En comparaison, La même partie dans un emballage CSP mesure 3,7 mmx3,8 mmx0,5 mm (7MM3). Autrement dit, vous pouvez réduire le volume par 85%. Ces économies peuvent être utilisées pour réduire la zone et l'épaisseur des PCB pour les appareils portables. Par conséquent, La demande d'appareils basés sur le WLCSP des appareils portables et de l'Internet des objets (IdO) Les fabricants ne se limitent pas à SRAM, Mais il y a une nouvelle demande.

LOGO UGPCB

LOGO UGPCB