チップパッケージ

IC PCB & 包装- ウェアラブルテクノロジーの未来について話すとき, ウェアラブルテクノロジーの革新の将来のコースは明らかです. 成功することは大声ではっきりしています, ウェアラブルエレクトロニクスは小さく、それでも実行する必要があります. この記事では、ウェーハの要件に焦点を当てています – レベルチップ – SRAMのレベルパッケージ .

フットプリントを減らすため, したがって、全体的なボードスペース, マイクロコントローラーは、他の世代ごとに小さなプロセスノードに移行します. 同時に, 彼らはより複雑で強力な操作を実行するために進化しています. 操作がより複雑になるにつれて, キャッシングを増やす必要があります. 残念ながら, 新しいプロセスノードごとに, 組み込みキャッシュの追加 (埋め込まれたsram) いくつかの理由で挑戦的になります, より高いserを含む, より低い収量, より高い消費電力. 顧客にはカスタムSRAM要件もあります. MCUメーカーがすべての可能なキャッシュサイズを提供するには、管理するには大きすぎる製品ポートフォリオが必要です. これにより、コントローラーコアに埋め込まれたSRAMを制限し、外部SRAMを介してキャッシュする必要がありました.

しかし, 外部SRAMが大量のPCBボードスペースを占有するため, 外部SRAMを使用すると、小型化の課題に直面します. その6つのトランジスタアーキテクチャのため, 外部SRAMをより小さなプロセスノードに移植することにより、外部SRAMのサイズを縮小すると、小型化された埋め込みSRAMを悩ませたのと同じ問題が導入されます.

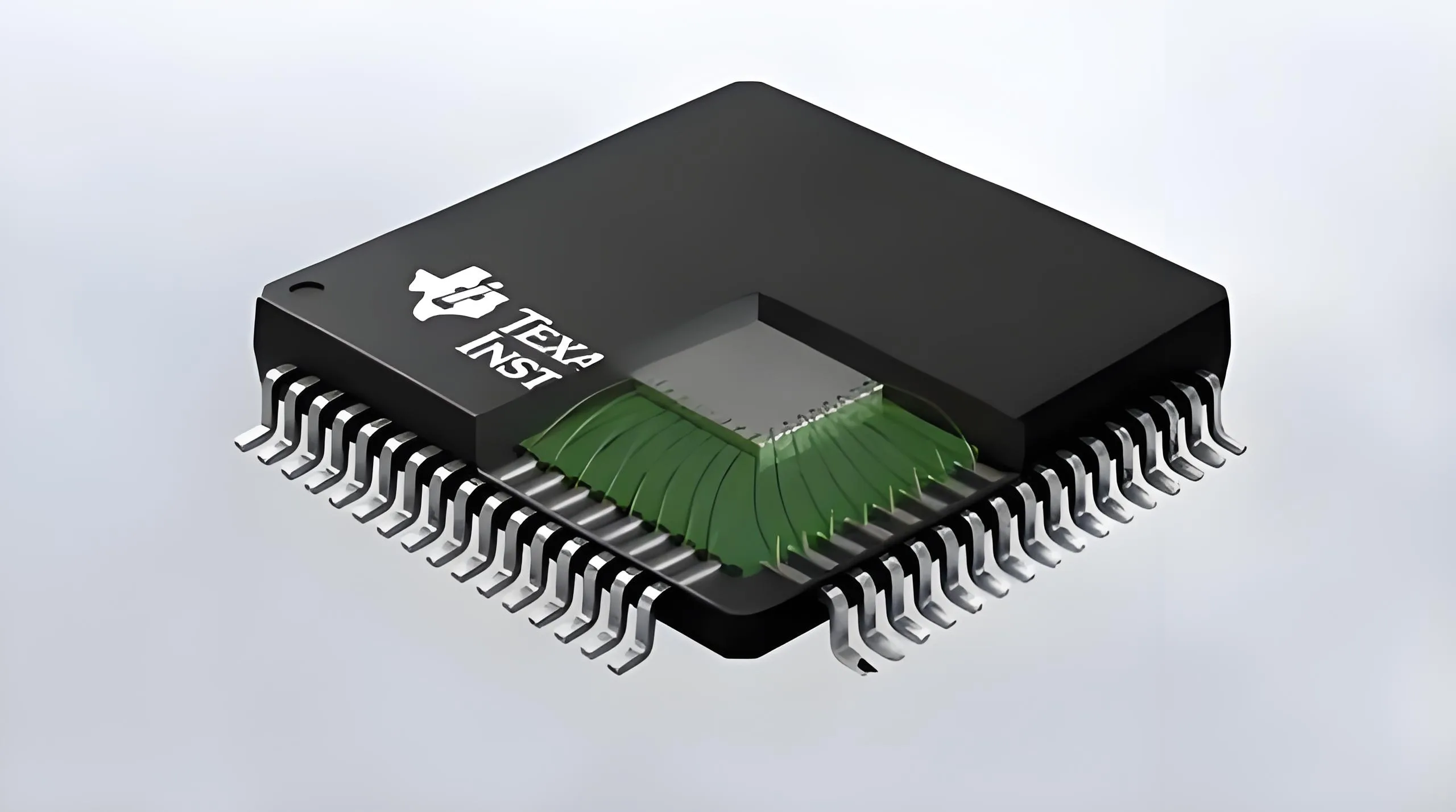

これは、この古くからの問題の次の代替手段に私たちをもたらします: 外部SRAMのチップパッケージングの比率をチップサイズに削減する. 通常, パッケージ化されたSRAMチップは、裸のチップのサイズの何倍も (まで 10 回). この問題の一般的な解決策は、カプセル化されたSRAMチップをまったく使用しないことです. SRAMチップを撮るのは理にかなっています (1/10 サイズ) 複雑なマルチチップパッケージを使用してMCUチップでパッケージ化します (MCP) または3Dパッケージテクノロジー (SIPシステムレベルのパッケージとしても知られています). しかし、このアプローチには多額の投資が必要であり、最大のメーカーにとってのみ実行可能です. デザインの観点から, SIPのコンポーネントが簡単に交換されないため、これも柔軟性を軽減します. 例えば, 新しいテクノロジーSRAMが利用可能な場合, SIPでSRAMチップを簡単に交換することはできません. パッケージ内の裸のチップを交換するには, SIP全体が再認証されなければなりません. 再認定には、再投資とより多くの時間が必要です.

そのため、MCPをトラブルにかけずにMCUからSRAMを除外しながらボードスペースを節約する方法があります? コアとチップのサイズ比に戻ります, 大幅な改善の余地があります. 金型にしっかりと収まるパッケージがあるかどうかを確認してみませんか? 言い換えると, 開梱できない場合, サイズスケールを減らしてください.

現在、最も高度なアプローチは、WLCSPを使用してチップパッケージのサイズを縮小することです (ウェーハレベルチップレベルパッケージ). WLCSPとは、個々のユニットをウェーハから小片に切断し、パッケージに組み立てる技術を指します. このデバイスは、基本的に、ボンディングラインまたは中間層接続を必要としない隆起したドットまたは球状配列パターンを備えた裸のチップです。. 仕様に応じて, チップレベルのパッケージの領域は順調に進んでいます 20% チップのそれよりも大きい. このプロセスは現在、製造工場がチップエリアを増やすことなくCSPコンポーネントを生産できる革新的なレベルに達しました。 (バンプ/球に合うように厚さがわずかに増加しているだけです).

数字. ウェーハ – の上 – チップパッケージ (WLCSP) パッケージ化された裸のサイズを縮小するための最先端の方法を提供します – チップ. ここに示されているWLCSPはDECA Technologiesによって開発されたものであり、それを構成するチップの領域を増やしません. (クレジット: DECAテクノロジー/サイプレス半導体)

CSPには、コーティングされていない映画よりもいくつかの利点があります. CSPデバイスのテストが簡単です, ハンドル, 組み立てる, 書き換えます. また、熱伝導性特性が強化されています. コアが新しいプロセスノードに転送されるとき, CSPサイズを標準化しながらコアを減らすことができます. これにより、CSPコンポーネントを、金型の変更に関連する合併症なしに、CSPコンポーネントの新世代に置き換えることができます。.

明らかに, これらのスペースの節約は、ウェアラブルとポータブルエレクトロニクスの需要の観点から重要です. 例えば, 今日の多くのウェアラブルデバイスでICメモリで使用されている48ボールBGAのサイズは8mmx6mmx1mmです (48mm3). 比較すると, CSPパッケージの同じ部分は、3.7mmx3.8mmx0.5mmです (7mm3). 言い換えると, ボリュームを減らすことができます 85%. この節約は、ポータブルデバイスのPCBエリアと厚さを減らすために使用できます. 結果として, ウェアラブルやモノのインターネットからのWLCSPベースのデバイスの需要 (IoT) メーカーはSRAMに限定されません, しかし、新しい需要があります.

UGPCBのロゴ

UGPCBのロゴ