TSV および TGV 3D パッケージング

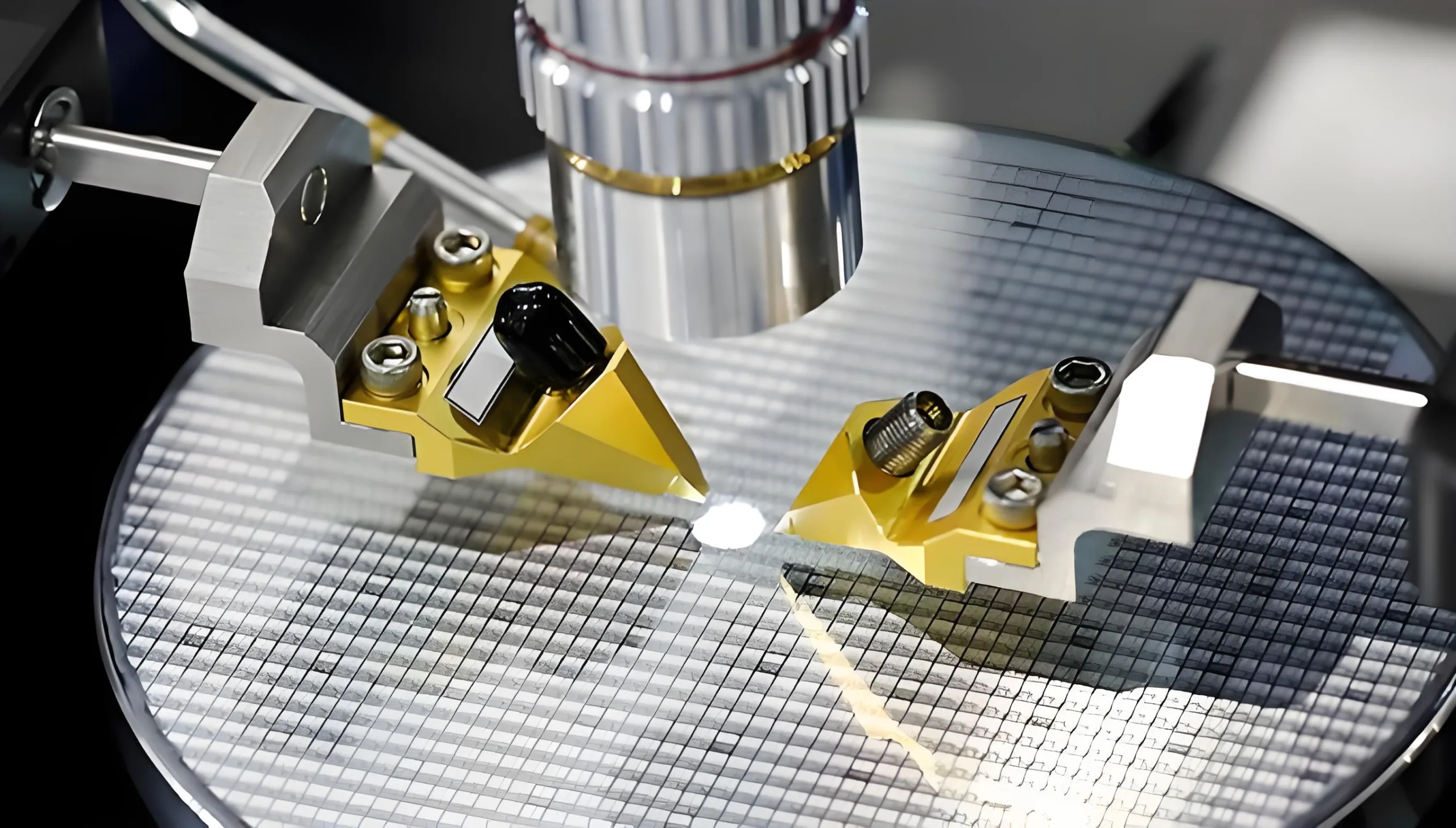

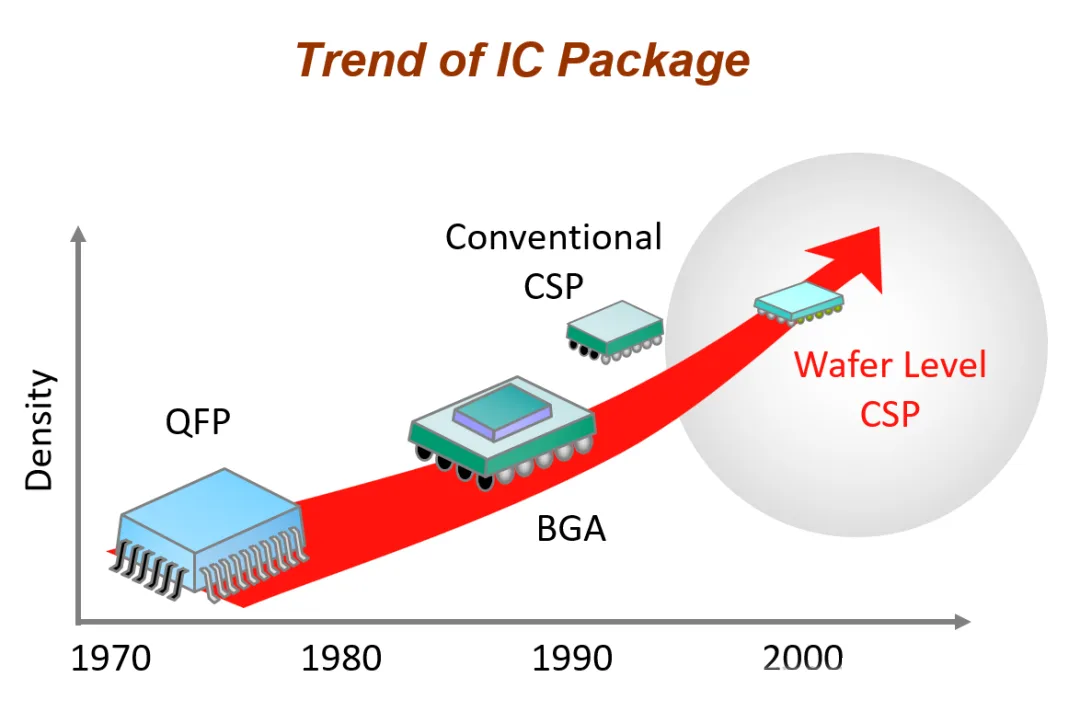

包装技術, 半導体産業の中核プロセスの一つとして, 小型化の傾向を目の当たりにしてきました, 高密度, 電子製品の多機能化. スルーホール実装から面実装実装へ, そしてBGAへ, CSP, SCM, MCM, WLP, 3Dパッケージ, およびSIP, パッケージング技術のあらゆる進歩が電子製品の大きな飛躍をもたらしました. これらのパッケージング技術の中には, シリコンビア経由 (TSV) およびガラス経由 (TGV) テクノロジーは間違いなく 3D パッケージングの新時代を開く 2 つの重要な鍵です.

3Dパッケージング技術の開発プロセス

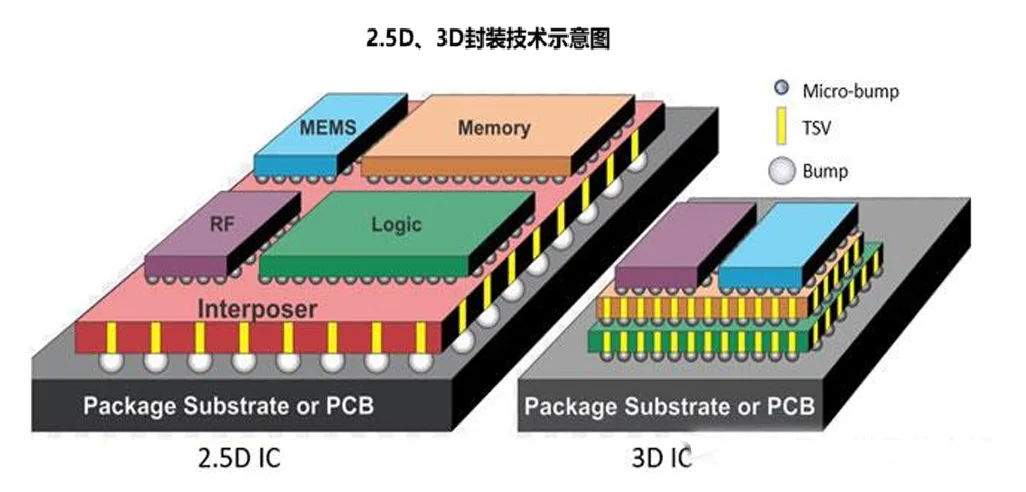

3D 包装: 形態と接続方法

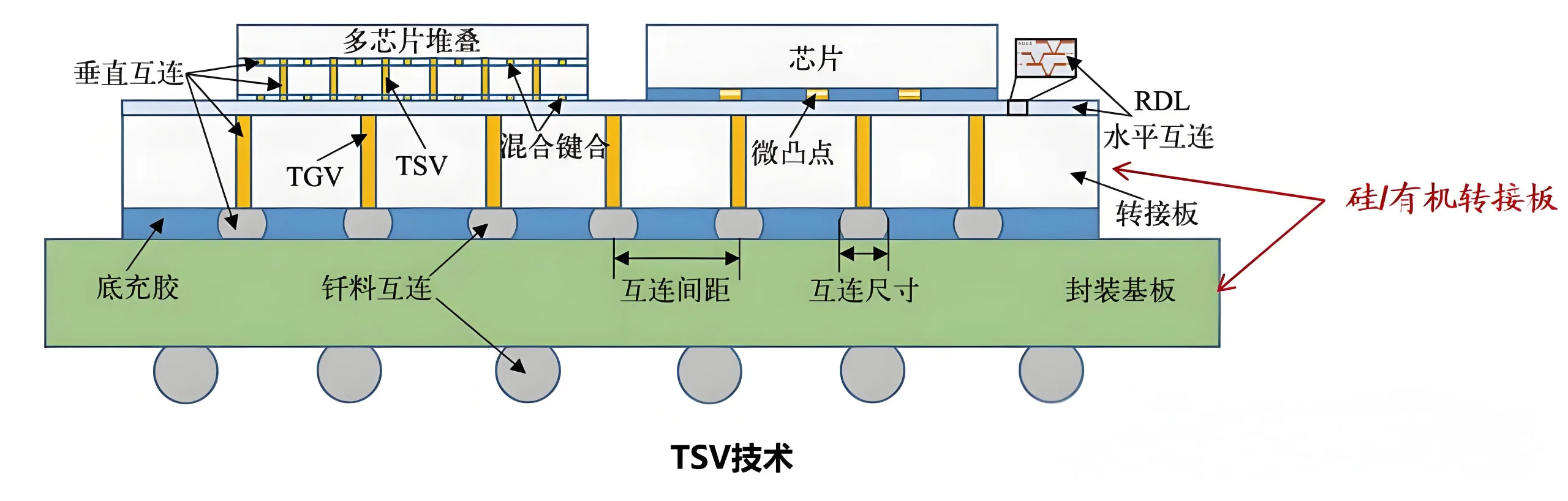

3Dパッケージは主に3つのタイプに分類されます: 埋設型, 活性基板タイプ, そしてスタックタイプ. 埋め込み型は多層配線内や基板内にデバイスを埋め込みます。. アクティブ基板タイプでは、最初にコンポーネントをウェハ基板と統合してアクティブ基板を形成します。, そして多層配線を配置します. 積層型はシリコンウェハやチップを積層するものです。. 3D 相互接続方法にはワイヤボンディングが含まれます, フリップチップ, TSV, および薄膜導体. その中で, TSVによりチップ間の垂直相互接続が可能, 小型化を実現する重要な技術, 高密度, 高性能, 異種構造パッケージングにおける多機能性.

3D実装技術の概念図

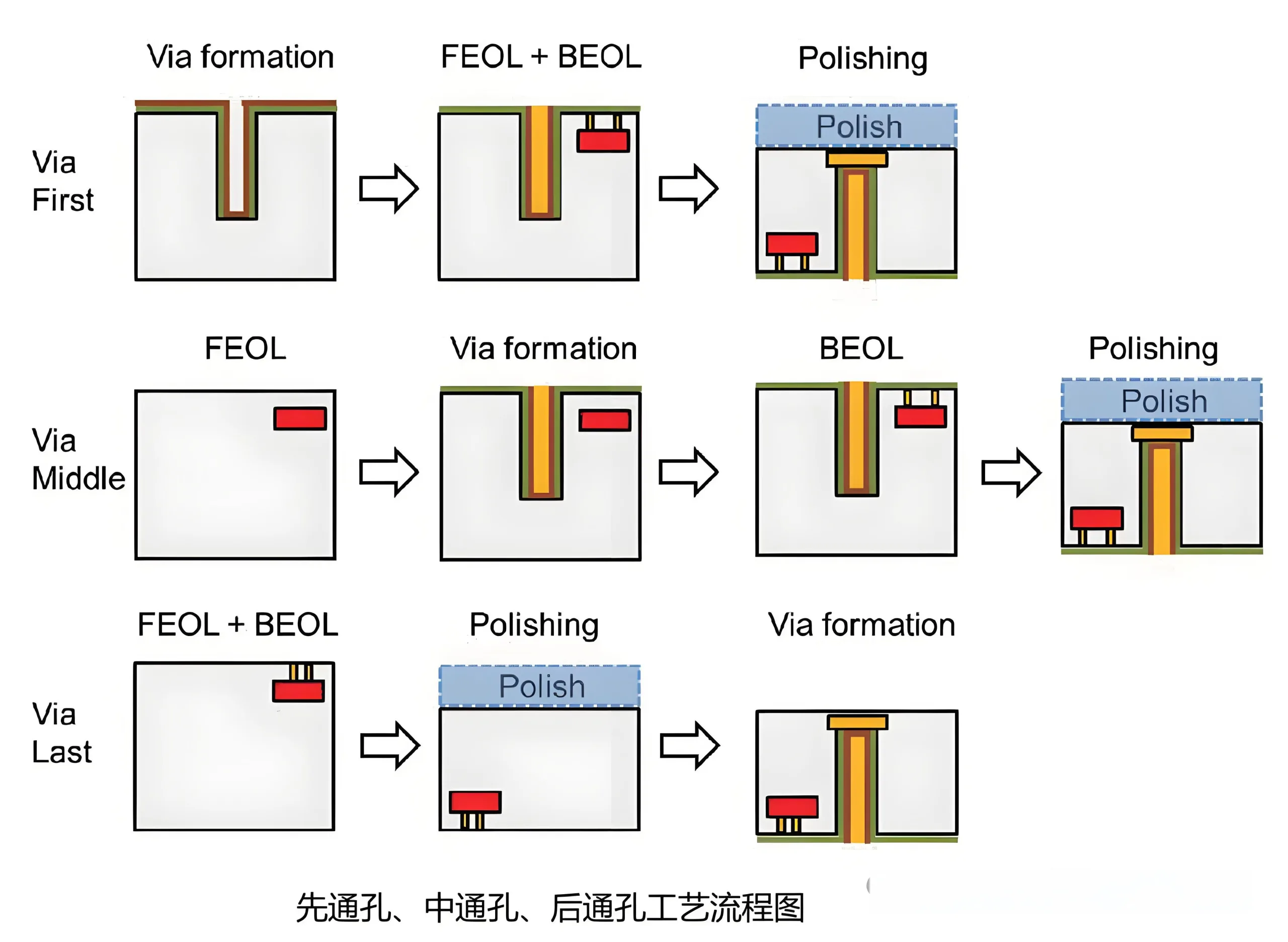

TSVテクノロジー: 工程と製造の流れ

TSV テクノロジーは基板を通る垂直信号経路を作成します, RDLの接続 (再配布層) 基板の上部と下部に, 3D導体経路の形成. フロントエンドオブラインのシーケンスに基づく (肉) そしてバックエンドオブライン (ベオル) プロセス, TSV プロセスは 3 つの主流の製造フローに分類できます。: ヴィアファースト, 中間経由, および ViaLast.

TSVテクノロジー: プロセスと製造手順

ビアエッチングプロセス

ビアエッチングプロセスはTSV構造の製造に重要です. 現在, 主流のエッチングプロセスは 4 つあります: ディープ反応性イオンエッチング (三つ), ウェットエッチング, 光補助電気化学エッチング (平和), そしてレーザー穴あけ加工.

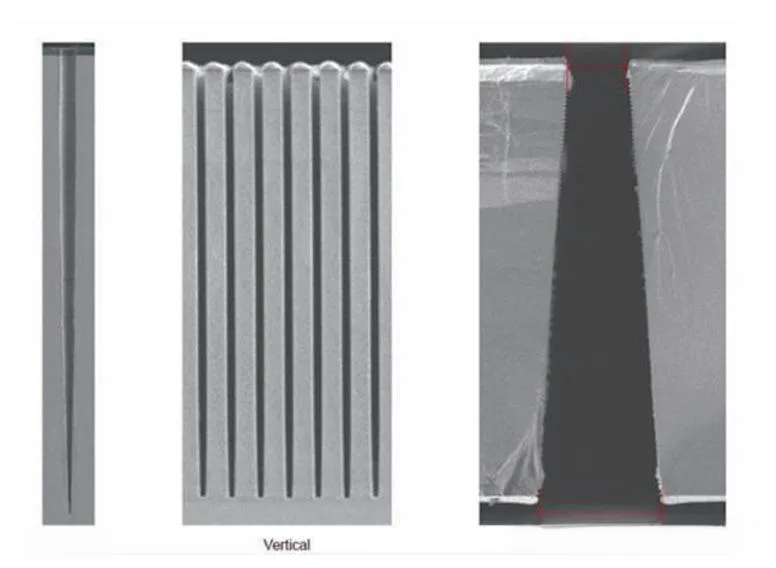

三つ

DRIEプロセスエッチングにより形成された高アスペクト比のスルーホール

高アスペクト比のビア構造を実現するために最も一般的に使用される TSV エッチング プロセス. ボッシュのプロセス, DRIE の改良版, 側壁のパッシベーション保護にSF6およびC4F8ガスを使用, 高アスペクト比のビアのエッチングに適しています. しかし, DRIE プロセスにより側壁の平滑性が低下する, 帆立貝状の欠陥の形成.

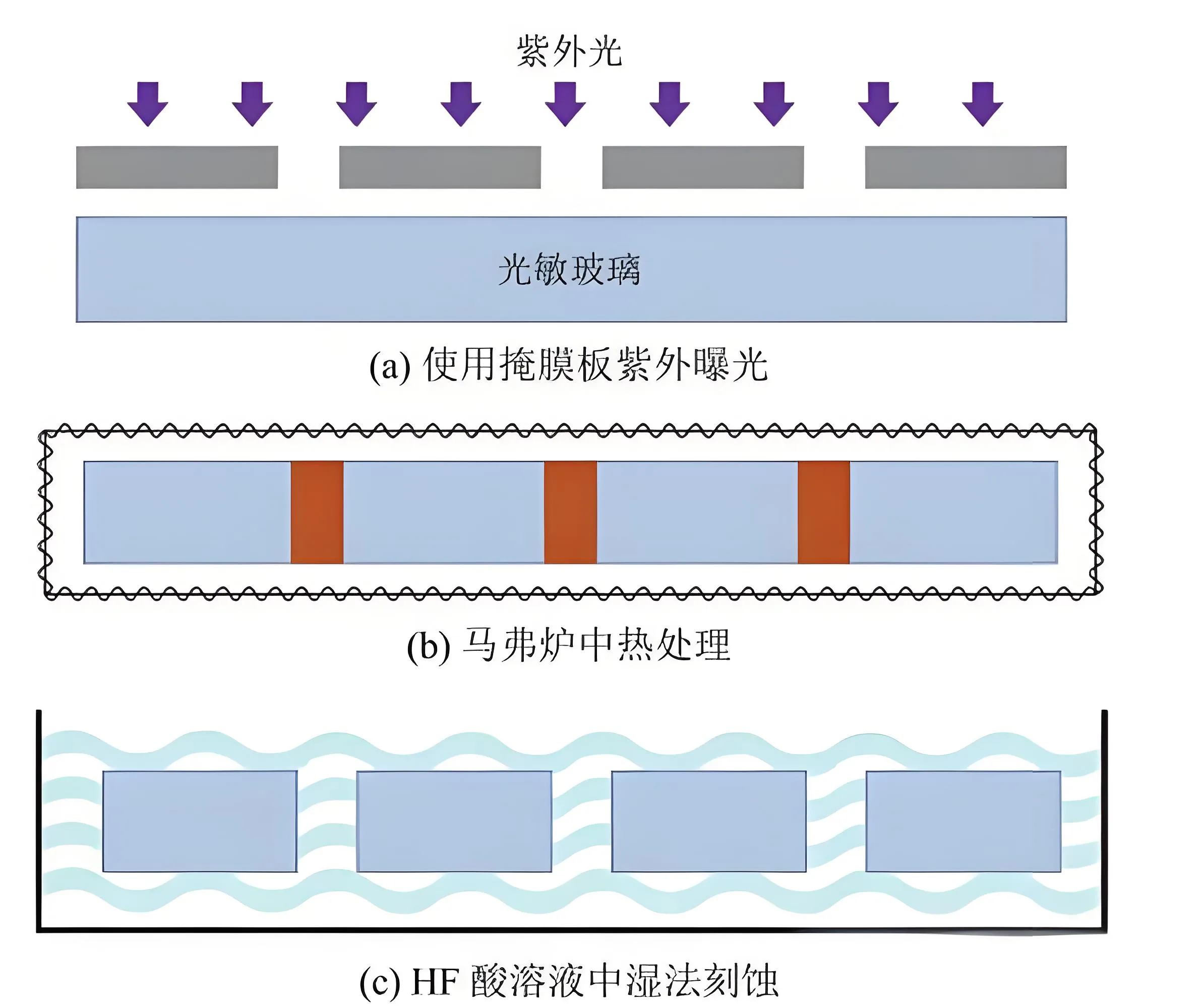

ウェットエッチング

ウェットエッチング

マスクと化学エッチングを組み合わせたもの, 工程がシンプルで低コストの大量生産に適しています。. しかし, シリコンウェーハの結晶方位の影響による, エッチングされたビアは垂直ではありません, 適用を制限する.

平和

紫外線を利用して電子-正孔対の生成を促進します, 電気化学エッチングプロセスの加速, 超高アスペクト比のビア構造のエッチングに適しています, ただしエッチング深さの制御性は劣る.

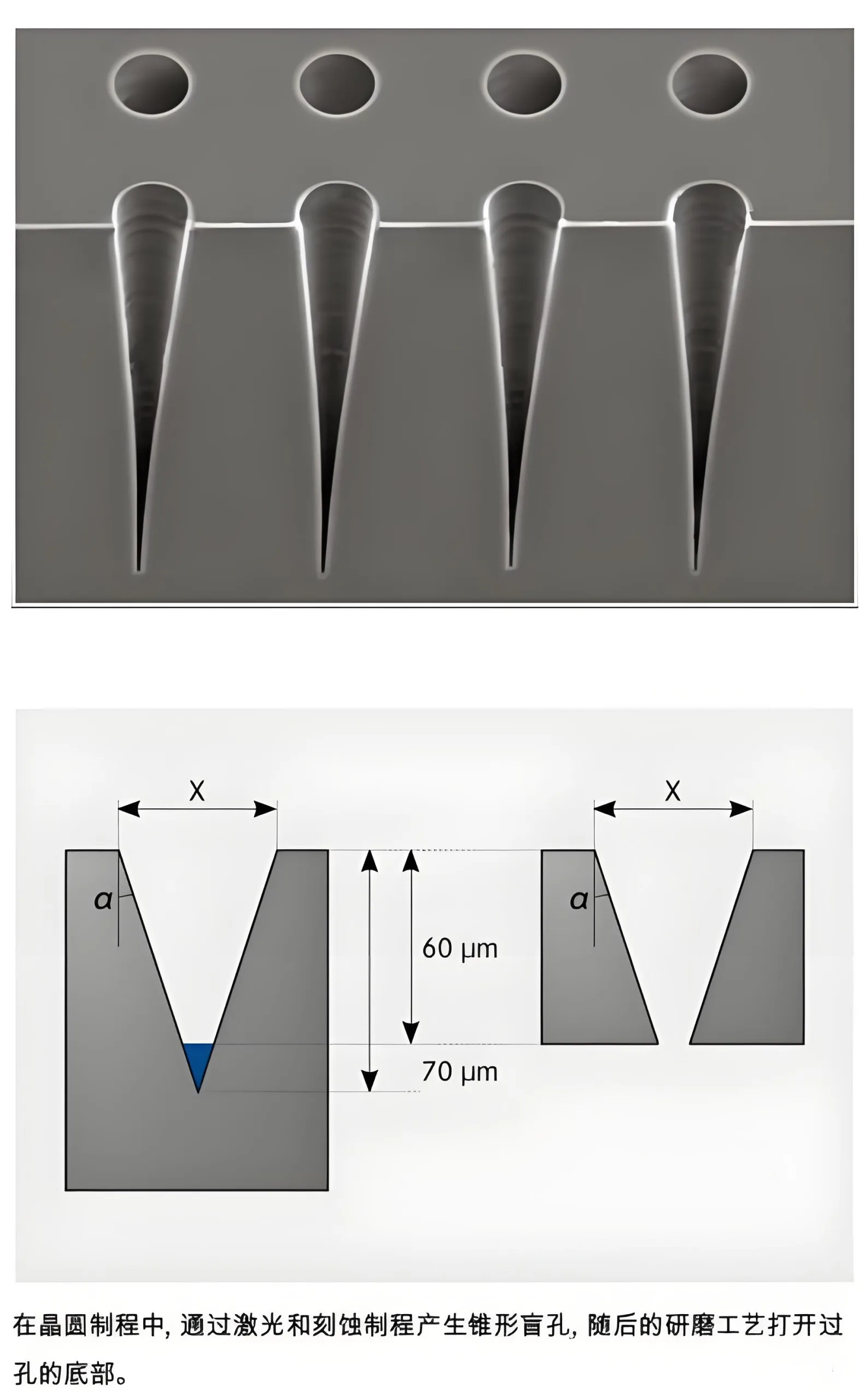

レーザー穴あけ加工

レーザー穴あけ加工

高エネルギーのレーザー光線を使用して、指定された領域の材料を溶解および蒸発させます。, 高アスペクト比の形成, 垂直側壁ビア, しかし、穴の壁は熱損傷を受けやすく、信頼性に影響します。.

シリコン貫通ビア技術

ライナー蒸着プロセス

ライナー堆積プロセスはビアエッチング後に実行されます. 蒸着されたライナー層, 通常はSiO2などの酸化物, 直流漏れを遮断する役割を果たします. 堆積プロセスは、絶縁層の絶縁破壊電圧要件を満たし、層間の強力な一貫性と良好な接着性を確保する必要があります。.

PECVD

SiO2 または SiNx を絶縁層として堆積するために使用されます。, ViaMiddle および ViaLast プロセスに適しています, BEOL 材料との互換性を確保する.

ALD

Al2O3を蒸着してより緻密な絶縁層を得る.

メタルフィル加工

TSV 充填プロセスが TSV の品質を決定します, 電気メッキ銅が主流の素材です. 電気めっき速度分布の違いに基づく, サブコンフォーマルに分けることができる, 等角的な, 超等角, およびボトムアップ電気めっき法.

コンフォーマル電気めっき

Cuイオンを均一に補給, ビア内のすべての位置で電気めっき速度を基本的に一定にする, 内側に縫い目を1つだけ残す.

超等角電気めっき

Cuイオンの供給を制御することで, 底部の充填率は他の位置よりわずかに高い, 継ぎ目をなくし、空隙のない充填を実現.

ボトムアップ電気めっき

底部を除いて電気めっき率はゼロに抑えられています。, 下から上に徐々に電気めっき, 電気めっき時間の短縮.

RDLプロセステクノロジー

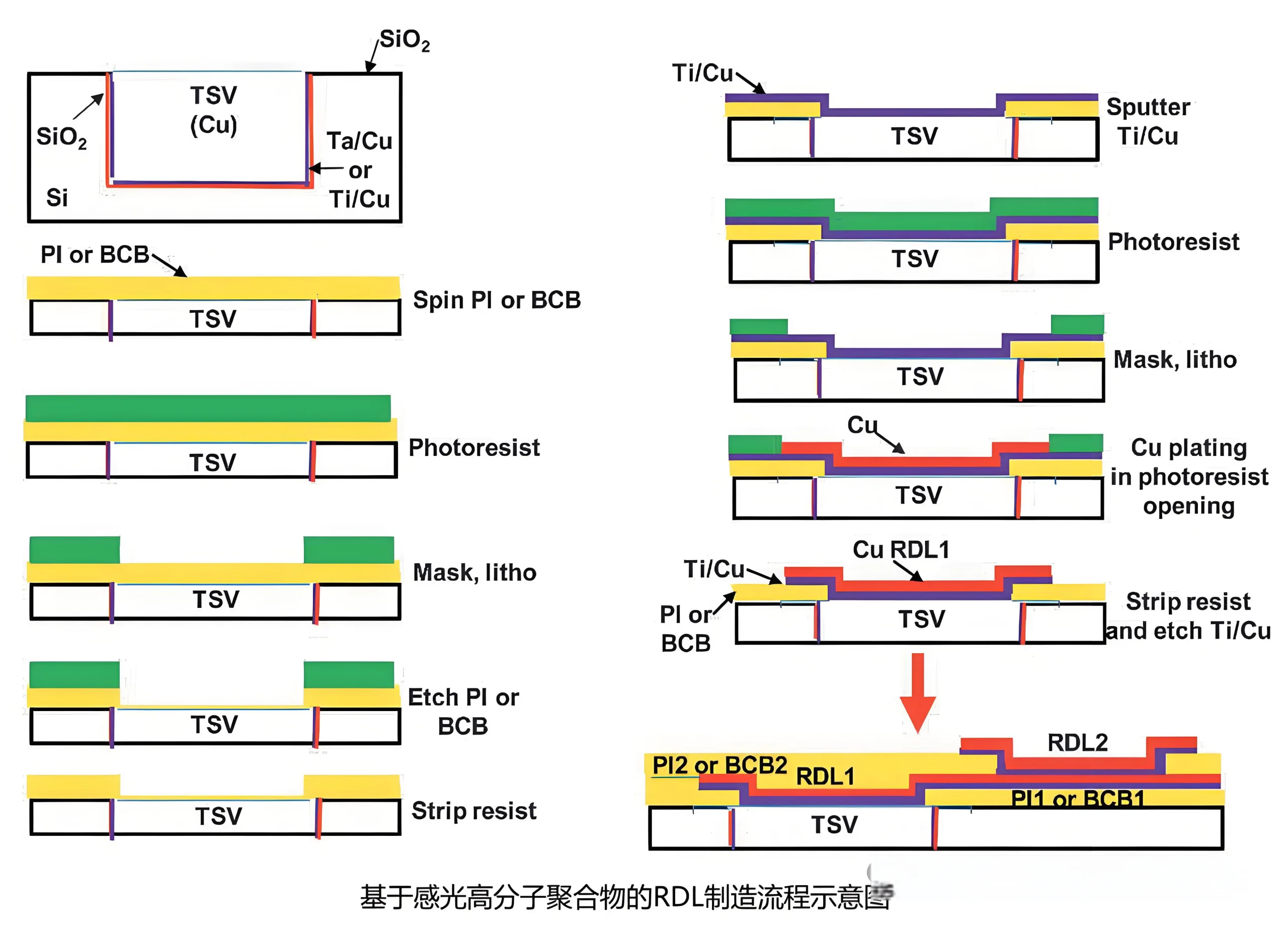

RDL技術は3D実装に欠かせない基礎技術です, ポートの再割り当てまたはパッケージ間の相互接続のためのメタル相互接続の作成に使用されます。. 主流の RDL プロセスは 2 つあります: 感光性ポリマーと銅ダマシンをベースとした.

RDL プロセスのフロー図

感光性ポリマーに基づく RDL プロセス

PI または BCB 樹脂のスピン コーティングが含まれます, フォトリソグラフィー, エッチング, Ti/Cuバリア/シード層のPVDスパッタリング, フォトリソグラフィーと銅電気めっきを組み合わせて RDL を製造します.

ダマシン加工あり

最初に絶縁層として SiO2 または Si3N4 を堆積します, フォトリソグラフィーとエッチングにより窓を形成します, Ti/Cuスパッタ, CMP を使用して希望の厚さにまで薄くします。.

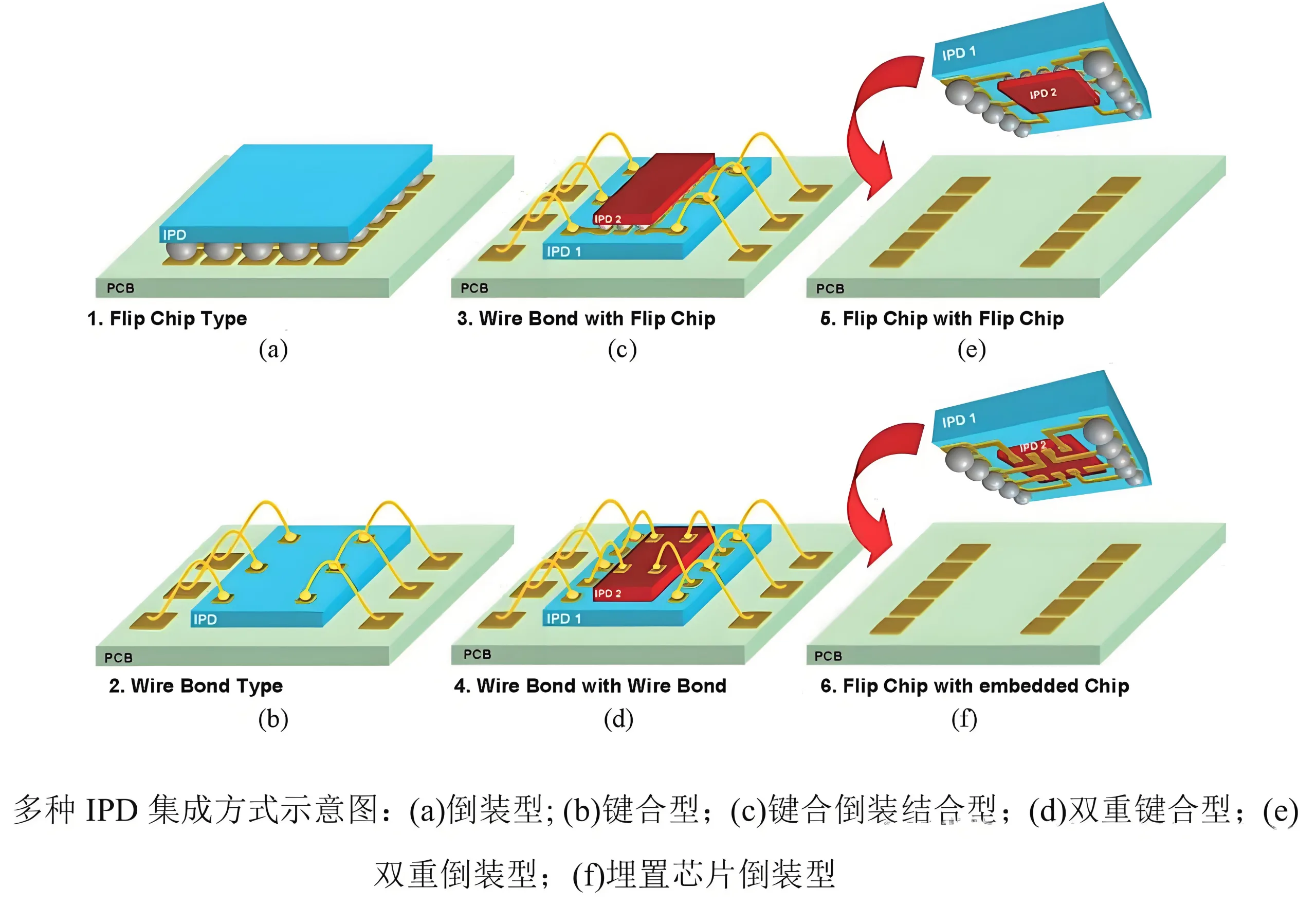

IPDプロセスとTGVテクノロジー: 3D パッシブデバイスの新たな道

統合された受動デバイス (IPD) このプロセスでは、受動デバイスを別の基板に統合することで、必要に応じて呼び出すことができる受動デバイスのライブラリを形成します。. IPD は低コストと高い柔軟性の利点を提供します, TSV 3D 受動デバイスの製造に特に適しています. IPDはさまざまな基板材料を使用可能, Siを含む, GaN, Al2O3セラミックス, ガラス基板, 等, 設計の自由度の拡大.

統合受動デバイスプロセス

3IPDおよびTGVプロセスに基づいて製造されたDインダクタは、従来の半導体材料と比較してガラス基板の抵抗率がはるかに高いため、優れた絶縁特性を示します。, 低い挿入損失を実現. さらに, MIMキャパシタはガラス基板IPD上に製造可能, TGV 3D インダクタと相互接続して 3D パッシブ フィルタ構造を形成.

結論

3Dパッケージングのキーテクノロジーとして, TSV および TGV 技術は、半導体パッケージング技術の革新を推進しただけでなく、小型化を強力にサポートしてきました。, 高密度, エレクトロニクス製品の高性能化、. 継続的な技術開発により、, TSV と TGV は将来の電子製品においてますます重要な役割を果たします, 3D パッケージングの新時代の到来. 継続的な探求と革新を通じて, TSV と TGV テクノロジーが人間をより賢くするだろうと信じる理由があります。, より便利な, 効率的な電子ライフスタイル.

UGPCBのロゴ

UGPCBのロゴ