칩 포장

IC PCB & 포장- 웨어러블 기술의 미래에 대해 이야기 할 때, 웨어러블 기술 혁신의 미래 과정은 분명합니다. 성공하는 것이 크고 분명합니다, 웨어러블 전자 제품은 작고 여전히 수행해야합니다. 이 기사는 웨이퍼 요구 사항에 중점을 둡니다 – 레벨 칩 – SRAM의 레벨 포장 .

발자국을 줄입니다, 따라서 전체 보드 공간, 마이크로 컨트롤러는 다른 세대마다 더 작은 프로세스 노드로 마이그레이션됩니다. 동시에, 그들은보다 복잡하고 강력한 운영을 수행하기 위해 진화하고 있습니다.. 운영이 더욱 복잡해짐에 따라, 캐싱을 증가시켜야 할 긴급한 필요성이 있습니다. 안타깝게도, 각각의 새로운 프로세스 노드와 함께, 임베디드 캐시 추가 (내장 된 SRAM) 여러 가지 이유로 도전이됩니다, 더 높은 ser 포함, 낮은 수율, 그리고 더 높은 전력 소비. 고객은 또한 맞춤형 SRAM 요구 사항이 있습니다. MCU 제조업체가 가능한 모든 캐시 크기를 제공하려면 관리하기에는 너무 큰 제품 포트폴리오가 있어야합니다.. 이로 인해 컨트롤러 코어에 포함 된 SRAM을 제한하고 외부 SRAM을 통해 캐시해야 할 필요성이 있습니다..

하지만, 외부 SRAM은 많은 양의 PCB 보드 공간을 차지하기 때문에, 외부 SRAM을 사용하면 소형화의 도전에 직면 해 있습니다. 6 번의 트랜지스터 아키텍처로 인해, 외부 SRAM을 더 작은 프로세스 노드로 포팅하여 외부 SRAM의 크기를 줄이면 소형 내장 SRAM을 괴롭힌 것과 동일한 문제가 발생합니다..

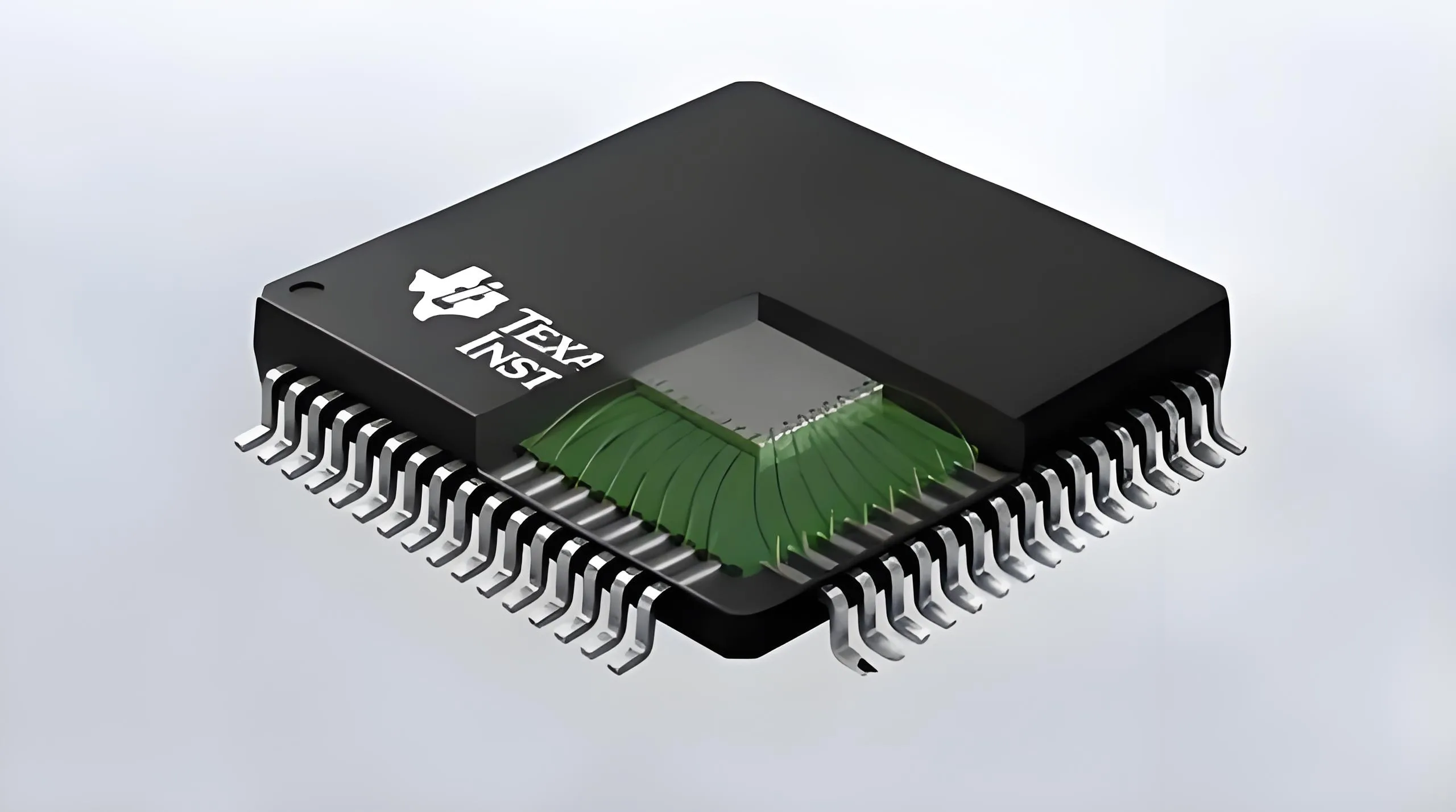

이것은 우리를이 오래된 문제에 대한 다음 대안으로 만듭니다.: 외부 SRAM에서 칩 포장 대 칩 크기의 비율 감소. 일반적으로, 포장 된 SRAM 칩은 베어 칩 크기의 여러 배입니다. (최대 10 타임스). 이 문제에 대한 일반적인 해결책은 캡슐화 된 SRAM 칩을 전혀 사용하지 않는 것입니다.. SRAM 칩을 가져가는 것이 합리적입니다 (1/10 크기) 그런 다음 복잡한 멀티 치프 포장을 사용하여 MCU 칩으로 패키지하십시오. (MCP) 또는 3D 포장 기술 (SIP 시스템 수준 포장으로도 알려져 있습니다). 그러나이 접근법은 상당한 투자가 필요하며 최대 규모의 제조업체에게만 가능합니다.. 디자인 관점에서, SIP의 구성 요소가 쉽게 교체되지 않기 때문에 유연성이 줄어 듭니다.. 예를 들어, 새로운 기술 SRAM을 사용할 수있는 경우, SIP에서 SRAM 칩을 쉽게 교체 할 수 없습니다. 패키지의 베어 칩을 교체하려면, 한 모금은 다시 인증되어야합니다. Requalification에는 재투자와 더 많은 시간이 필요합니다.

MCP를 곤경에 빠뜨리지 않고 MCU에서 SRAM을 제외하면서 보드 공간을 절약 할 수있는 방법이 있습니까?? 코어 대 칩 크기 비율로 돌아갑니다, 우리는 상당한 개선의 여지를 볼 수 있습니다. 곰팡이에 꽉 끼는 패키지가 있는지 확인하지 않는 이유는 무엇입니까?? 다시 말해서, 포장을 풀 수 없다면, 크기 규모를 줄이십시오.

현재 가장 진보 된 접근 방식은 WLCSP를 사용하여 칩 패키지의 크기를 줄이는 것입니다. (웨이퍼 레벨 칩 레벨 패키지). WLCSP는 개별 장치를 웨이퍼에서 작은 조각으로 자른 다음 패키지로 조립하는 기술을 말합니다.. 이 장치는 본질적으로 본딩 라인 또는 중간 층 연결이 필요하지 않은 도트 또는 구형 어레이 패턴이있는 베어 칩입니다.. 사양에 따라, 칩 레벨 패키지의 영역은 최대입니다 20% 칩보다 큽니다. 프로세스는 이제 제조 플랜트가 칩 영역을 늘리지 않고 CSP 구성 요소를 생산할 수있는 혁신적인 수준에 도달했습니다. (범프/구체에 맞게 두께가 약간 증가하면).

숫자. 웨이퍼 – ~에 – 칩 포장 (ulc) 포장 된 베어의 크기를 줄이기위한 가장 진보 된 방법을 제공합니다. – 칩. 여기에 표시된 WLCSP는 DECA Technologies에 의해 개발되었으며이를 구성하는 칩의 영역을 증가시키지 않습니다.. (신용 거래: DECA 기술/ 사이프러스 반도체)

CSP는 코팅되지 않은 필름에 비해 몇 가지 장점이 있습니다. CSP 장치는 테스트하기가 더 쉽습니다, 핸들, 모으다, 다시 쓰십시오. 또한 열전도율이 향상됩니다. 코어가 새로운 프로세스 노드로 전송 될 때, CSP 크기를 표준화하면서 코어를 줄일 수 있습니다.. 이를 통해 CSP 구성 요소는 곰팡이 변경과 관련된 합병증없이 새로운 세대의 CSP 구성 요소로 대체 될 수 있습니다..

확실히, 이러한 공간 절약은 웨어러블 및 휴대용 전자 장치에 대한 수요 측면에서 중요합니다.. 예를 들어, 오늘날 많은 웨어러블 장치에서 IC 메모리에 사용되는 48 볼 BGA의 크기는 8mmx6mmx1mm입니다. (48MM3). 이에 비해, CSP 패키지의 동일한 부분은 3.7mmx3.8mmx0.5mm입니다 (7MM3). 다시 말해서, 볼륨을 줄일 수 있습니다 85%. 이 절약은 휴대용 장치의 PCB 면적과 두께를 줄이는 데 사용될 수 있습니다.. 결과적으로, 웨어러블 및 사물 인터넷에서 WLCSP 기반 장치에 대한 수요 (IoT) 제조업체는 SRAM에만 국한되지 않습니다, 그러나 새로운 수요가 있습니다.

UGPCB 로고

UGPCB 로고