웨이퍼에서 개별 단위를 절단한 후 패키징하는 기술은 수십 년 동안 반도체 집적 회로 패키징의 표준이었습니다.. 하지만, 높은 제조 비용과 오늘날 모듈의 RF 구성 요소 증가로 인해 이 접근 방식은 현재 주요 반도체 제조업체에서 채택되지 않고 있습니다.. 따라서, 웨이퍼 레벨 패키징의 등장 (WLP) 저가형 포장재 개발의 패러다임 전환을 가져왔습니다.. WLP는 웨이퍼 패키징 장치를 절단하기 전의 웨이퍼 레벨 패키징 기술입니다..

표준 도구 및 프로세스 사용, WLP는 웨이퍼 제조 공정의 확장 역할을 합니다.. 결국, 제조된 WLP DIE에는 칩 표면에 금속 패드가 있고 웨이퍼를 절단하기 전에 각 패드에 솔더 도트가 증착됩니다.. 이것, 차례로, WLP를 기존 PCB 조립 공정과 호환시키고 웨이퍼 자체에서 장치 테스트를 가능하게 합니다.. 결과적으로, 상대적으로 비용이 저렴하고 효율적인 프로세스입니다., 특히 웨이퍼 크기가 증가하고 칩 DIE가 축소됨에 따라. 웨이퍼의 크기는 지난 수십 년 동안 증가해 왔습니다., ~에서 4, 6, 그리고 8 직경 인치 12 신장. 이로 인해 웨이퍼당 DIE 수가 증가합니다., 제조 비용을 낮추는 것. 전기적 성능 측면에서, WLP는 다른 패키징 기술보다 우수합니다., WLP 장치가 고밀도 RF 모듈에 통합되면, 장치와 PCB 사이의 상호 연결이 상대적으로 짧기 때문에 EM 기생 결합이 크게 감소합니다., 일부 유형의 CSP 기술에 사용되는 와이어 본드 상호 연결과 달리.

WLP 칩 플립칩 기술

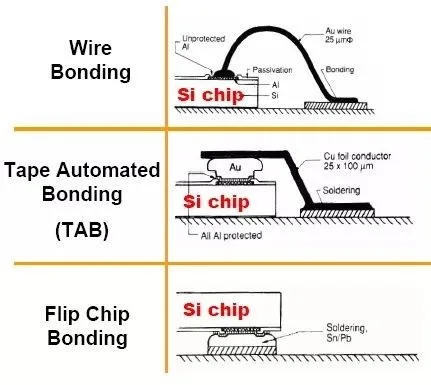

플립칩 기술, 제어형 축소 칩 연결이라고도 함 (C4), 1960년대 IBM이 개발한 여러 칩 조립 기술 중 하나입니다.. 와이어 본딩 기반 패키징 기술은 하드웨어 제작 후 실험실 디버깅을 위한 자유 유도 기능 측면에서 더 유연하지만, 또한 좋은 열전도율을 제공합니다., 플립칩 패키징 기술에 솔더 벌지를 사용하면 패키지 기판과 칩 사이의 전기적 연결이 상대적인 크기 감소를 제공합니다., 대기 시간 감소, 입력 및 출력 핀 측면에서 더 나은 절연. 수치 1 기판 위의 칩 DIE의 기본 구조를 보여줍니다., 칩 표면에서 성장하는 Cu 기둥 상단에 솔더 볼이 있음. 솔더 조인트는 일반적으로 솔더 조인트에 대한 기계적 지지를 제공하기 위해 필러 몰드 화합물로 캡슐화됩니다..

WLP 칩 플립칩 기술

WLP 칩 레벨 패키지

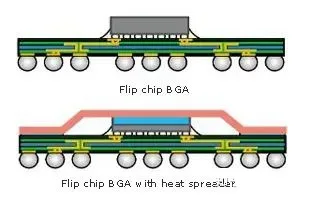

칩 스케일 포장 (CSP) 마이크로 전자공학 및 반도체 산업에서 가장 일반적으로 사용되는 패키징 방법 중 하나입니다.. 마이크로칩 제조업체는 이미 여러 유형의 CSP 기술을 사용할 수 있지만, 새로운 기능과 새로운 응용 분야별 제품을 지원하는 제품에 대한 수요를 충족하기 위해 새로운 유형이 계속해서 등장하고 있습니다.. 이러한 포장 요구 사항은 필요한 신뢰성 수준에 따라 달라질 수 있습니다., 비용, 추가 기능, 그리고 전체적인 사이즈. 이름에서 알 수 있듯이, CSP의 패키지 크기는 칩 DIE 크기와 거의 동일합니다., 이것이 주요 장점 중 하나입니다. WLP 제조 공정을 채택하여, CSP는 가능한 가장 작은 패키지-다이 크기 비율을 달성하기 위해 지속적으로 개발되고 있습니다.. 그림과 같이 2, 볼 그리드 배열 (BGA) 패키지의 CSP 스타일은 PCB 배선을 단순화하면서 여러 상호 연결을 허용합니다., PCB 조립 처리량 증가 및 제조 비용 절감.

웨이퍼 레벨 패키징

기타 캡슐화 기술

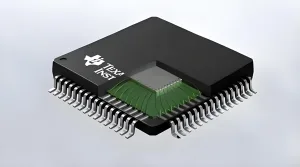

애플리케이션 맞춤형 모듈 패키지에 완벽하게 통합할 수 있는 여러 가지 다른 형태의 통합 IC 패키징이 있습니다.. 쿼드 플랫 패키지 (MFF) 최초의 표면 실장 IC 패키지 기술 중 하나입니다.,패키지 구조는 확장된 상호 연결 리드가 있는 4개의 측면으로 구성됩니다., 그림과 같이 3(에이). 돌출된 리드는 패키지 프레임에 연결되어 금속-절연체-금속을 형성합니다. (밈) 리드와 칩 사이의 유형 커패시터 DIE 금속, 일치하는 요소로 사용할 수 있는. 이 기술은 패키지의 주변 핀 수가 다음보다 많을 수 있는 밀리미터 크기의 IC에 적합합니다. 100 다리. 이러한 유형의 캡슐화에는 여러 파생물이 있습니다., 사용된 재료에 따라, 세라믹 쿼드플랫팩 등, 얇은 쿼드 플랫 팩, 플라스틱 쿼드 플랫 팩, 플라스틱 쿼드 플랫 팩) 및 메탈 쿼드 플랫 팩 (MQFP). QFN, 쿼드 플랫 무연, 그림에 표시된. 3(비) 평평한 구리 리드 프레임과 라디에이터의 열 전달 패드로 사용되는 플라스틱 패키지로 구성된 여러 표면 실장 패키징 기술 중 하나입니다.. 와이어 본딩은 상호 연결에도 사용할 수 있습니다., 본드 라인은 도체일 뿐만 아니라 인덕터이기도 하기 때문에, 일반적으로 이 캡슐화 기술을 사용하는 장치의 성능에 영향을 미칩니다., 전체 디자인의 일부로 간주되지 않는 한. QFN은 4개의 면으로 구성된 인터커넥트이지만, 복엽기 unled 리드 (DFN) 또한 상호 연결 평면 리드의 양쪽 측면이 나타나서 형성됩니다..

UGPCB 로고

UGPCB 로고