TSV 및 TGV 3D 패키징

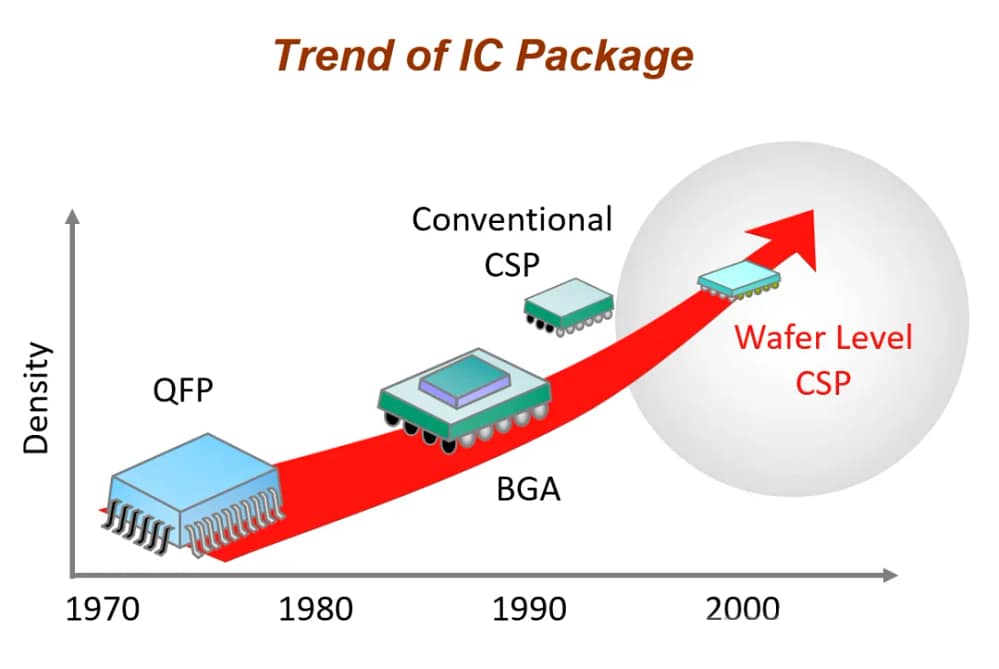

포장기술, 반도체 산업의 핵심 공정 중 하나로, 소형화 추세를 목격했습니다., 고밀도, 전자 제품의 다기능성. 스루홀 패키징에서 표면 실장 패키징까지, 그리고 BGA로, CSP, SCM, MCM, WLP, 3D 포장, 및 SIP, 패키징 기술의 모든 발전은 전자 제품의 획기적인 도약을 가져왔습니다.. 이러한 패키징 기술 중, 실리콘 비아를 통해 (TSV) 및 유리를 통해 (떼제베) 기술은 의심할 여지 없이 3D 패키징의 새로운 시대를 여는 두 가지 핵심 열쇠입니다..

3D 패키징 기술 개발 과정

3D 포장: 형태 및 상호연결 방식

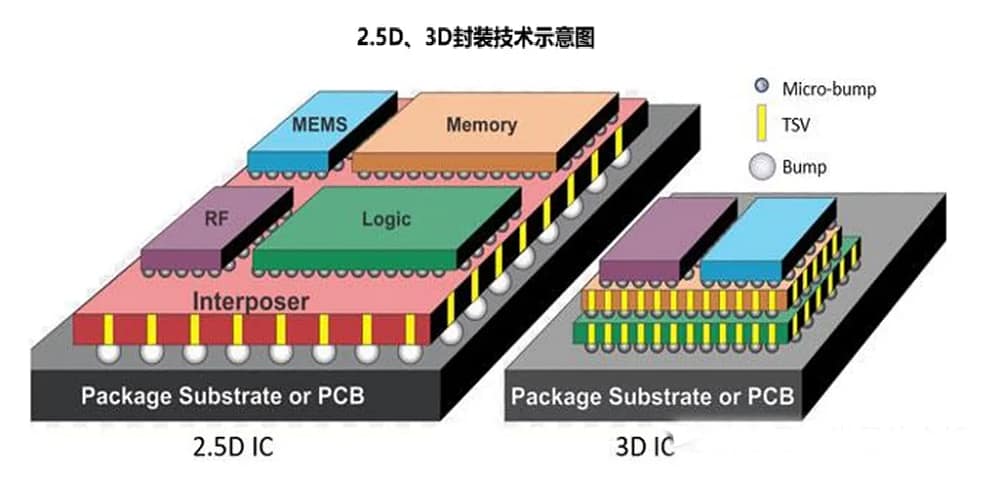

3D 포장은 크게 세 가지 유형으로 분류됩니다.: 매설형, 활성 기판 유형, 그리고 스택형. 매립형은 다층 배선 내부 또는 기판 내부에 장치를 매립합니다.. 능동 기판 유형은 먼저 구성요소를 웨이퍼 기판과 통합하여 능동 기판을 형성합니다., 그런 다음 다층 상호 연결을 배열합니다.. 적층형은 실리콘 웨이퍼나 칩을 적층하는 방식이다.. 3D 상호 연결 방법에는 와이어 본딩이 포함됩니다., 플립칩, TSV, 및 박막 도체. 그 중, TSV는 칩 간의 수직 상호 연결을 가능하게 합니다., 소형화를 위한 핵심 기술로 작용, 고밀도, 고성능, 이종 구조 패키징의 다기능성.

3D 패키징 기술의 개략도

TSV 기술: 공정 및 제조 흐름

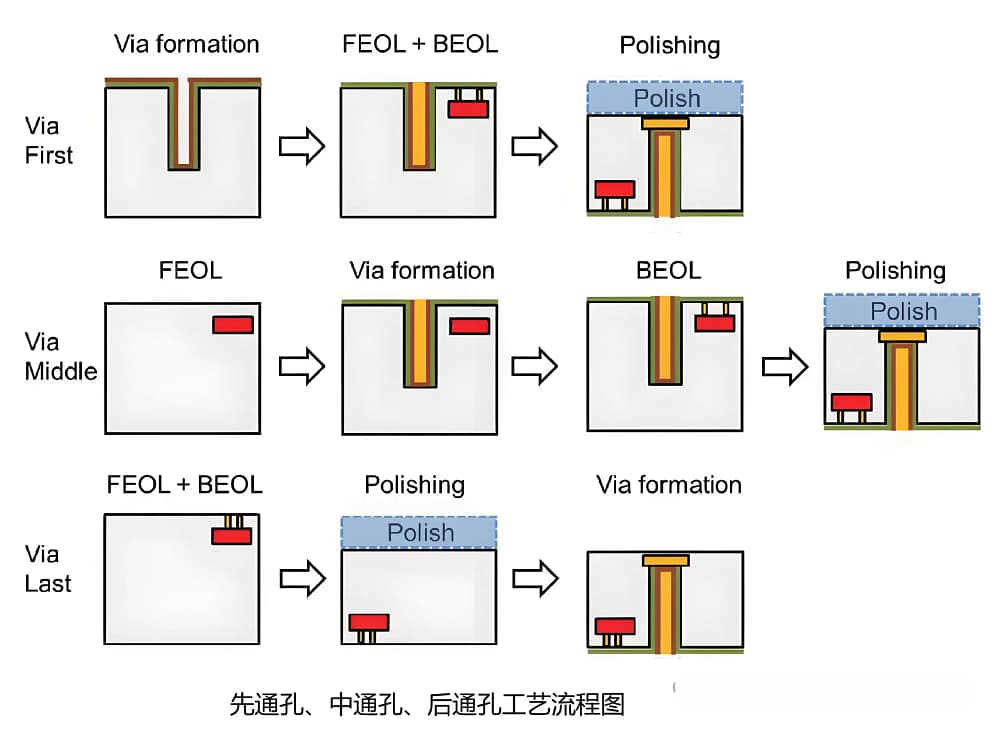

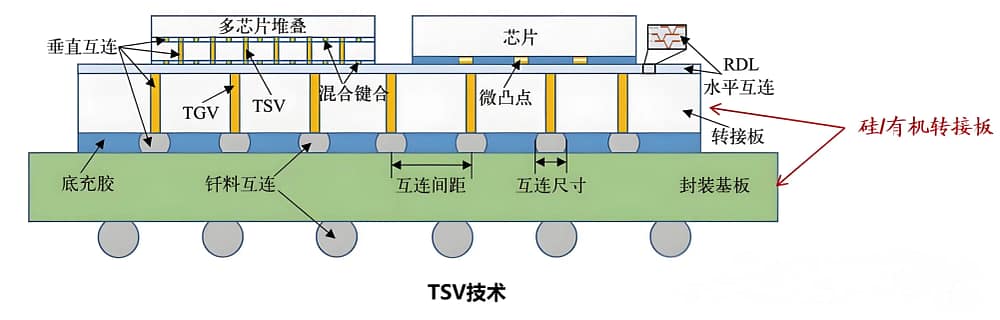

TSV 기술은 기판을 통해 수직 신호 경로를 생성합니다., RDL 연결 (재배포 계층) 기판의 상단과 하단에, 3D 도체 경로 형성. FLO(Front-End-of-Line) 순서를 기반으로 함 (고기) 그리고 백엔드 라인 (벌) 프로세스, TSV 프로세스는 세 가지 주요 제조 흐름으로 나눌 수 있습니다.: 비아퍼스트, 비아미들, 및 ViaLast.

TSV 기술: 공정 및 제조절차

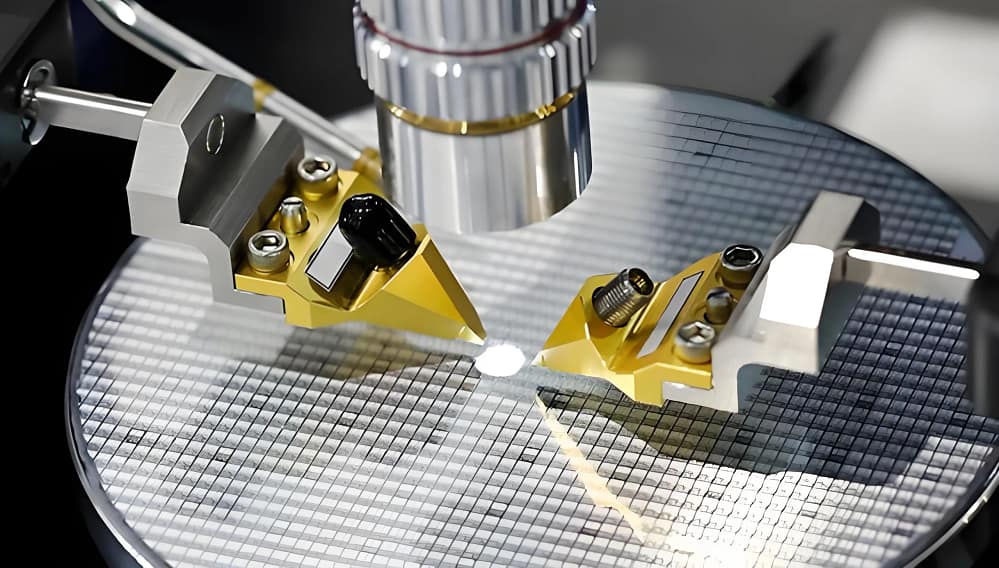

에칭 공정을 통해

TSV 구조 제조에는 비아 에칭 공정이 중요합니다.. 현재, 네 가지 주류 에칭 공정이 있습니다.: 깊은 반응성 이온 에칭 (삼), 습식 에칭, 광 보조 전기화학 에칭 (평화), 그리고 레이저 드릴링.

삼

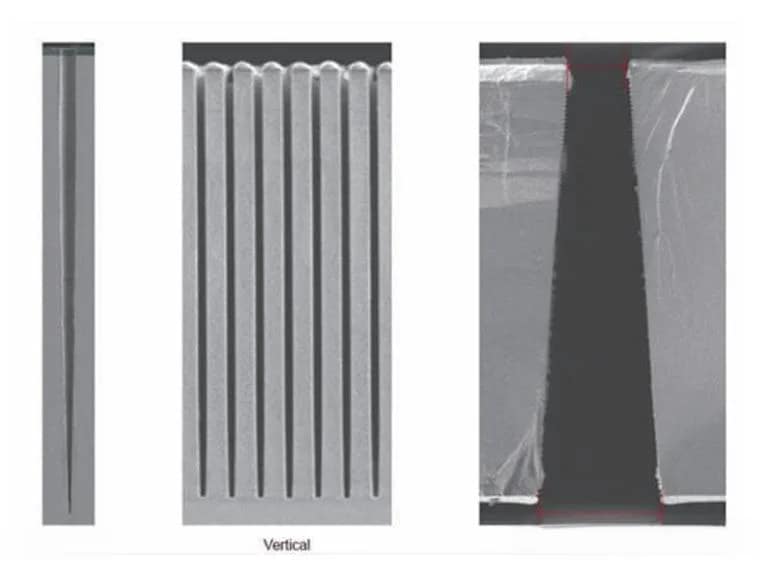

DRIE 공정 에칭으로 형성된 고종횡비 스루홀

비아 구조를 통해 높은 종횡비를 달성하기 위해 가장 일반적으로 사용되는 TSV 에칭 공정. 보쉬 프로세스, DRIE의 향상된 버전, 측벽 패시베이션 보호를 위해 SF6 및 C4F8 가스를 사용합니다., 높은 종횡비의 비아 에칭에 적합. 하지만, DRIE 공정으로 인해 측벽 매끄러움이 좋지 않음, 가리비 모양의 결함 형성.

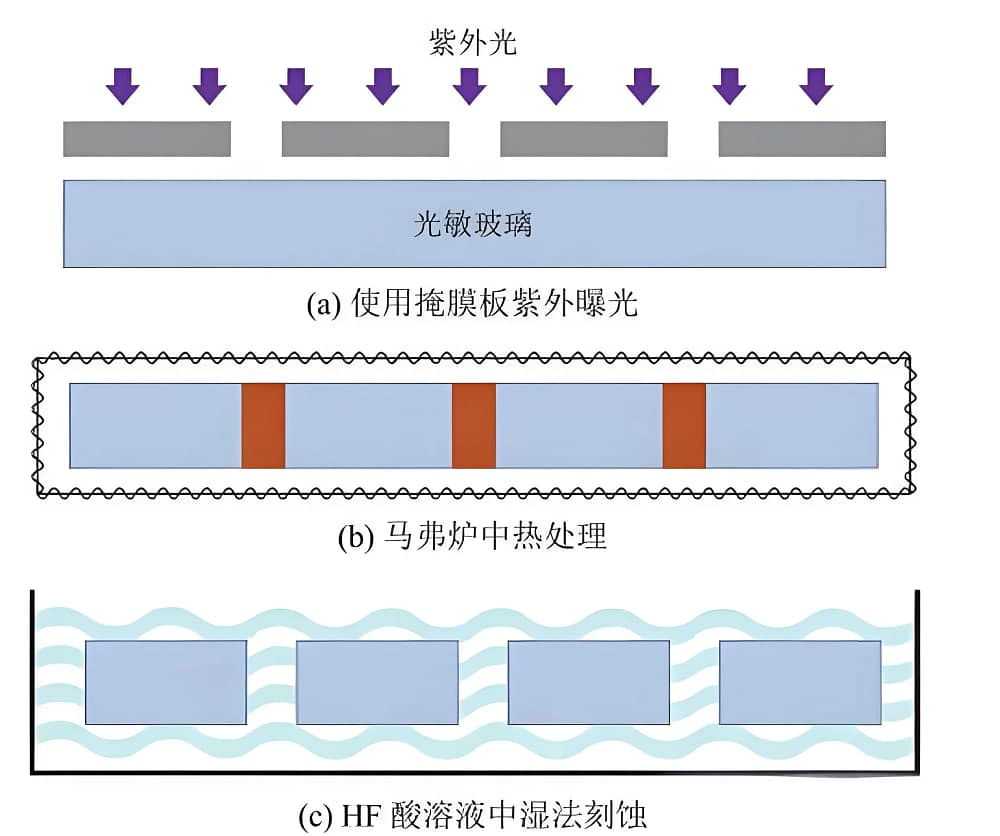

습식 에칭

습식 에칭

마스크와 화학적 에칭을 결합합니다., 공정이 간단하고 저비용 대량생산에 적합. 하지만, 실리콘 웨이퍼 결정학적 방향의 영향으로 인해, 에칭된 비아가 수직이 아닙니다., 적용을 제한.

평화

자외선을 이용하여 전자-정공 쌍 생성을 가속화합니다., 전기화학적 에칭 공정 가속화, 초고종횡비 비아 구조 에칭에 적합, 그러나 에칭 깊이 제어 가능성이 약함.

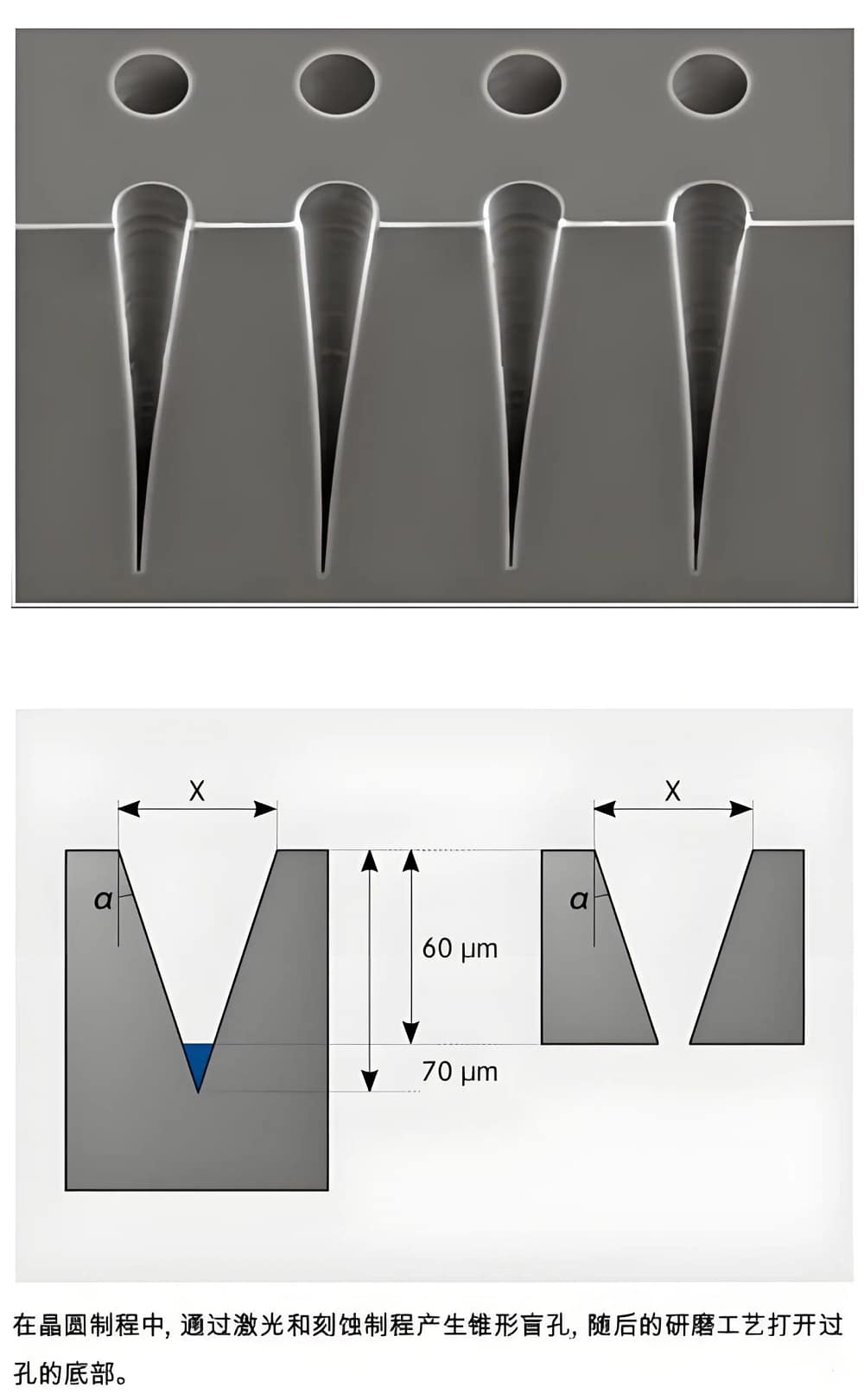

레이저 드릴링

레이저 드릴링

고에너지 레이저빔을 이용해 특정 부위의 물질을 녹이고 증발시키는 방식, 높은 종횡비 형성, 수직 측벽 비아, 그러나 구멍 벽은 신뢰성에 영향을 미치는 열 손상에 취약합니다..

실리콘 관통 비아 기술

라이너 증착 공정

라이너 증착 공정은 via Etching 후 진행됩니다.. 증착된 라이너 층, 일반적으로 SiO2와 같은 산화물, 직류 누설을 차단하는 역할을 합니다.. 증착 공정은 절연층의 항복 전압 요구 사항을 충족해야 하며 강력한 일관성과 층 간 우수한 접착력을 보장해야 합니다..

PECVD

절연층으로 SiO2 또는 SiNx를 증착하는 데 사용됩니다., ViaMiddle 및 ViaLast 프로세스에 적합, BEOL 재료와의 호환성 보장.

ALD

밀도가 높은 절연층을 얻기 위해 Al2O3를 증착합니다..

금속 충전 공정

TSV 채우기 프로세스가 TSV 품질을 결정합니다., 전기도금된 구리가 주류 재료임. 전기도금율 분포의 차이에 기초, subconformal로 나눌 수 있다, 등각의, 슈퍼컨포멀, 및 상향식 전기 도금 방법.

컨포멀 전기도금

Cu 이온의 균일한 보충 보장, 기본적으로 비아 내의 모든 위치에서 전기도금 속도를 일관되게 만듭니다., 안쪽에 솔기를 하나만 남겨두고.

슈퍼컨포멀 전기도금

Cu 이온의 공급을 조절함으로써, 하단 충전율은 다른 위치보다 약간 높습니다., 솔기를 제거하고 공극 없는 충전 달성.

상향식 전기도금

전기 도금 속도는 바닥을 제외하고 0으로 억제됩니다., 점차적으로 바닥에서 상단까지 전기 도금, 전기도금 시간 단축.

RDL 프로세스 기술

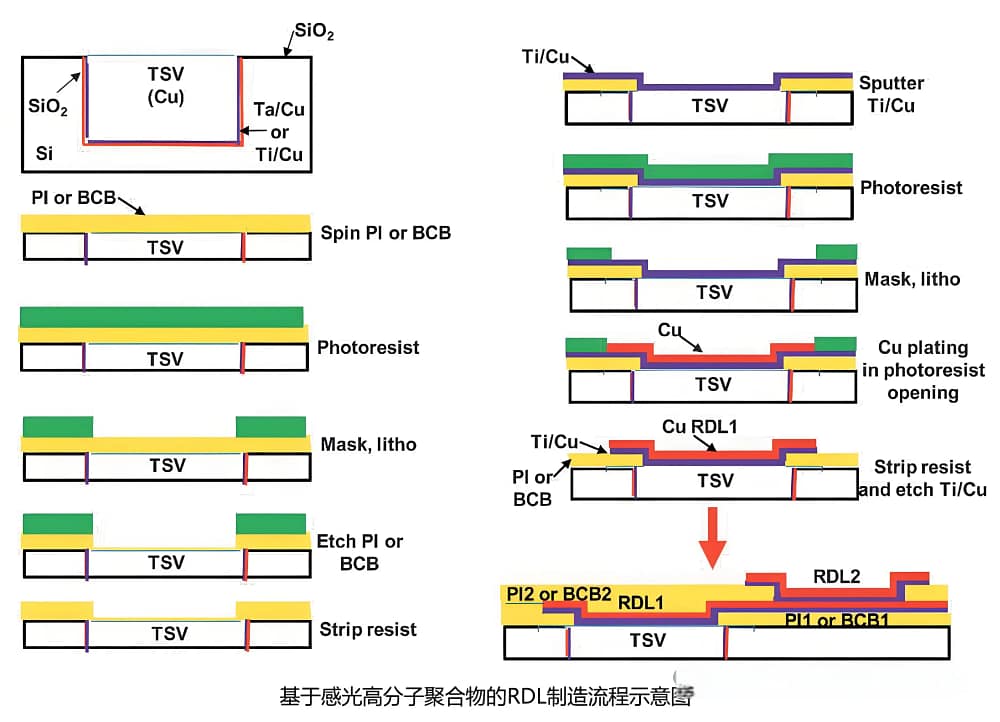

RDL 기술은 3D 패키징에 필수적인 기초기술이다., 포트 재할당 또는 패키지 간 상호 연결을 위한 금속 상호 연결을 만드는 데 사용됩니다.. 두 가지 주요 RDL 프로세스가 있습니다.: 감광성 폴리머와 Cu 다마신 기반.

RDL 프로세스 흐름 다이어그램

감광성 폴리머 기반 RDL 공정

스핀코팅 PI 또는 BCB 수지 사용, 포토리소그래피, 에칭, Ti/Cu 배리어/시드층의 PVD 스퍼터링, 포토리소그래피와 Cu 전기도금을 결합하여 RDL을 제조합니다..

다마신 프로세스 포함

먼저 절연층으로 SiO2 또는 Si3N4를 증착합니다., 포토리소그래피와 에칭을 통해 창 형성, Ti/Cu 스퍼터, CMP를 이용해 원하는 두께로 줄여줍니다..

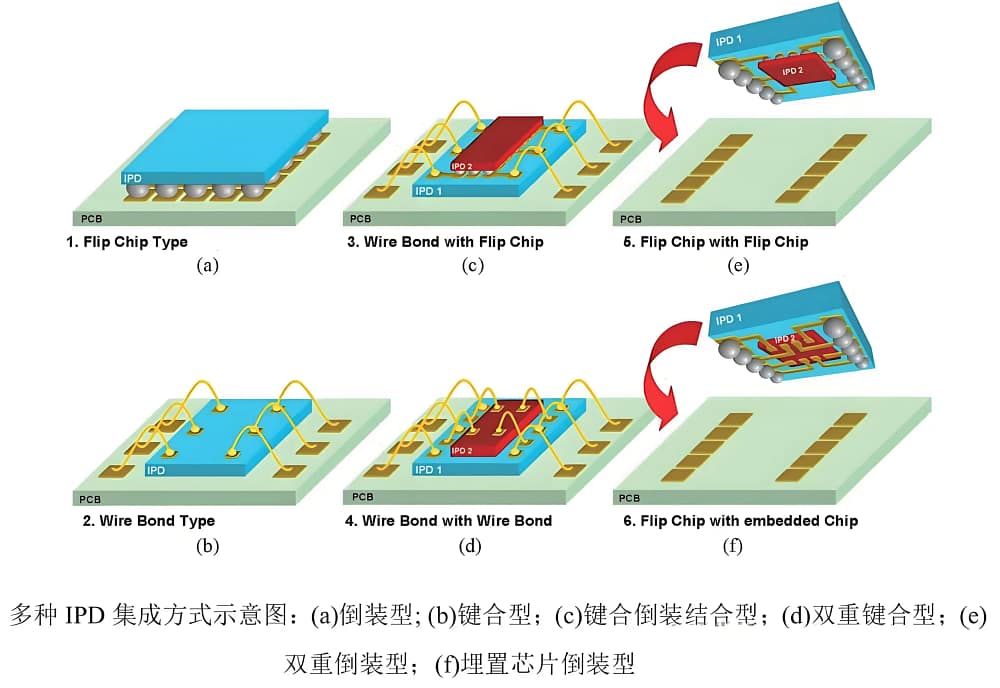

IPD 프로세스 및 TGV 기술: 3D 수동소자를 위한 새로운 길

통합 수동 장치 (IPD) 프로세스는 수동 장치를 별도의 기판에 통합하여 필요에 따라 호출할 수 있는 수동 장치 라이브러리를 형성합니다.. IPD는 저렴한 비용과 높은 유연성의 장점을 제공합니다., TSV 3D 수동 소자 제조에 특히 적합. IPD는 다양한 기판 재료를 사용할 수 있습니다., Si를 포함한, GaN, Al2O3 세라믹, 유리 기판, 등., 설계 유연성 확대.

통합 수동 소자 프로세스

3IPD 및 TGV 공정을 기반으로 제작된 D 인덕터는 기존 반도체 소재에 비해 유리 기판의 저항률이 훨씬 높아 우수한 절연 특성을 나타냅니다., 삽입 손실이 적음. 추가적으로, MIM 커패시터는 유리 기판 IPD에서 제작 가능, TGV 3D 인덕터와 상호 연결되어 3D 수동 필터 구조를 형성합니다..

결론

3D 패키징의 핵심 기술로, TSV와 TGV 기술은 반도체 패키징 기술의 혁신을 주도했을 뿐만 아니라 소형화를 강력히 뒷받침해 왔습니다., 고밀도, 전자제품의 고성능화와. 지속적인 기술개발로, TSV와 TGV는 미래 전자 제품에서 점점 더 중요한 역할을 할 것입니다, 3D 패키징의 새로운 시대를 열다. 끊임없는 탐구와 혁신을 통해, 우리는 TSV와 TGV 기술이 인간을 더욱 스마트하게 만들 것이라고 믿을 이유가 있습니다., 더 편리하다, 효율적인 전자 라이프 스타일.

UGPCB 로고

UGPCB 로고