embalagem de chip

IC PCB & Embalagem- Ao falar sobre o futuro da tecnologia vestível, O futuro curso da inovação tecnológica vestível é clara. É alto e claro que ter sucesso, Os eletrônicos vestíveis devem ser pequenos e ainda executar. Este artigo se concentra nos requisitos de bolacha – chip de nível – embalagem nivelada em sram .

Para reduzir a pegada, e assim o espaço geral da placa, Os microcontroladores migram para nós de processo menores a todas as outras gerações. Ao mesmo tempo, Eles estão evoluindo para executar operações mais complexas e poderosas. À medida que as operações se tornam mais complexas, há uma necessidade urgente de aumentar o cache. Infelizmente, com cada novo nó de processo, Adicionando cache incorporado (SRAM incorporado) torna -se desafiador por vários motivos, Incluindo SER mais alto, menor rendimento, e maior consumo de energia. Os clientes também têm requisitos de SRAM personalizados. Para que os fabricantes de MCU forneçam todos os tamanhos possíveis de cache, exigiriam que eles tenham um portfólio de produtos que é muito grande para gerenciar. Isso impulsionou a necessidade de limitar o SRAM incorporado no núcleo do controlador e para armazená -lo através de um SRAM externo.

No entanto, Como o SRAM externo ocupa uma grande quantidade de espaço na placa de PCB, O uso de SRAM externo enfrenta o desafio da miniaturização. Devido à sua arquitetura de seis transistores, Reduzir o tamanho do SRAM externo, portando o SRAM externo para um nó de processo menor, introduzirá os mesmos problemas que atormentaram o SRAM incorporado miniaturizado.

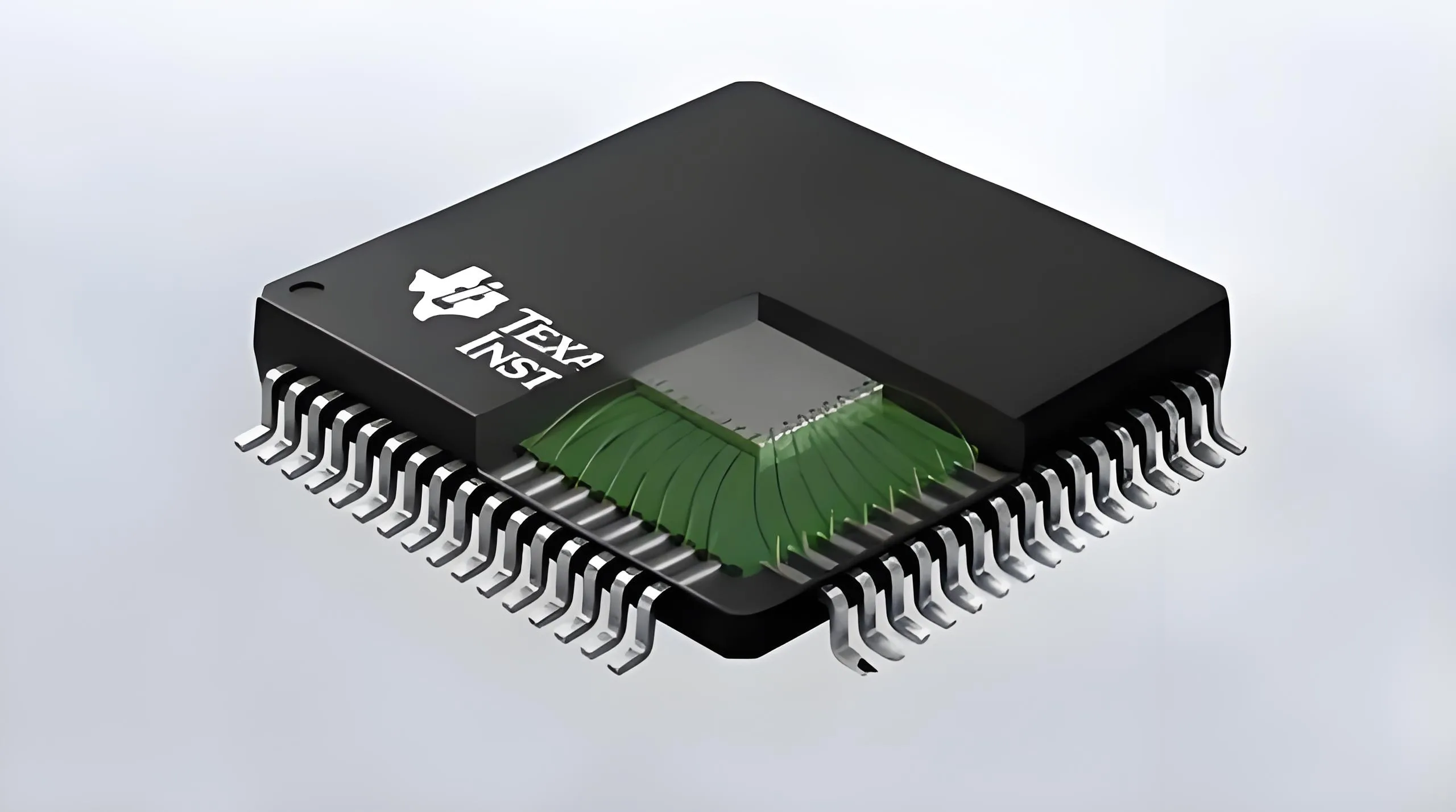

Isso nos leva à próxima alternativa a esse problema antigo: reduzindo a proporção de embalagens de chip para o tamanho do chip no SRAM externo. Tipicamente, Os chips SRAM embalados são muitas vezes do tamanho do chip nu (até 10 vezes). Uma solução comum para esse problema é não usar chips sram encapsulados. Faz sentido pegar um chip SRAM (1/10 tamanho) e depois empacote-o com um chip MCU usando embalagens multi-chip complexas (MCP) ou tecnologia de embalagem 3D (também conhecido como embalagem no nível do sistema SIP). Mas essa abordagem requer investimento significativo e só é viável para os maiores fabricantes. De uma perspectiva de design, Isso também reduz a flexibilidade porque os componentes no SIP não são facilmente substituídos. Por exemplo, Se a nova tecnologia SRAM estiver disponível, Não podemos substituir facilmente o chip SRAM no SIP. Para substituir qualquer um dos chips nus no pacote, Todo o gole deve ser autenticado. A requalificação requer reinvestimento e mais tempo.

Então, existe uma maneira de salvar o espaço da placa enquanto exclui o SRAM do MCU sem colocar o MCP em apuros? Voltando à proporção de tamanho central para chip, Vemos espaço para melhorias significativas. Por que você não verifica se há um pacote que se encaixa bem no molde? Em outras palavras, Se você não pode descompactar, Reduza a escala de tamanho.

Atualmente, a abordagem mais avançada é reduzir o tamanho do pacote de chip usando o WLCSP (pacote de nível de lastro de bolas de bolas). WLCSP refere -se à tecnologia de cortar unidades individuais de uma bolacha em pedaços pequenos e depois montá -los em um pacote. O dispositivo é essencialmente um chip nu com um ponto elevado ou padrão de matriz esférica que não requer linhas de ligação ou conexões de camada intermediária. Dependendo das especificações, A área de um pacote de nível de lasca está fazendo 20% maior que o do chip. O processo agora atingiu um nível inovador, onde as fábricas podem produzir componentes CSP sem aumentar a área de chip (com apenas um ligeiro aumento de espessura para se encaixar no solavanco/esfera).

Números. Wafer – sobre – embalagem de chip (Ulc) Fornece o método mais avançado para reduzir o tamanho dos embalados – chip. O WLCSP mostrado aqui foi desenvolvido pela Deca Technologies e não aumenta a área dos chips que o compõem. (Crédito: Deca Technologies/ Cypress Semiconductor)

CSP tem algumas vantagens sobre o filme não revestido. Os dispositivos CSP são mais fáceis de testar, lidar, montar, e reescrever. Eles também têm propriedades de condutividade térmica aprimoradas. Quando o núcleo é transferido para nós de processo mais recentes, É possível reduzir o núcleo enquanto padroniza o tamanho do CSP. Isso garante que os componentes CSP possam ser substituídos por uma nova geração de componentes CSP sem complicações associadas à alteração do molde.

Obviamente, Essas economias espaciais são importantes em termos de demanda por wearables e eletrônicos portáteis. Por exemplo, O BGA de 48 bolas usado na memória IC em muitos dispositivos vestíveis hoje tem um tamanho de 8mmx6mmx1mm (48mm3). Por comparação, A mesma parte em um pacote CSP mede 3,7mmx3.8mx0.5mm (7mm3). Em outras palavras, Você pode reduzir o volume por 85%. Essa economia pode ser usada para reduzir a área de PCB e a espessura para dispositivos portáteis. Como resultado, A demanda por dispositivos baseados em WLCSP de wearables e Internet of Things (IoT) Fabricantes não se limitam a SRAM, Mas há uma nova demanda.

LOGOTIPO UGPCB

LOGOTIPO UGPCB