Чип -упаковка

IC PCB & Упаковка- Говоря о будущем носимой технологии, Будущий курс носимых технологических инноваций ясен. Громко и ясно, что добиться успеха, Носимая электроника должна быть маленькой и до сих пор выполнять. Эта статья фокусируется на требованиях к пластине – ровный чип – Уровень упаковки в SRAM .

Чтобы уменьшить след, И, таким образом, Микроконтроллеры мигрируют в более мелкие узлы процесса на каждом другом поколении. В то же время, Они развиваются, чтобы выполнить более сложные и мощные операции. По мере того, как операции становятся более сложными, Существует срочно увеличить кэширование. К сожалению, с каждым новым узлом процесса, Добавление встроенного кеша (Встроенный SRAM) становится сложным по ряду причин, в том числе высший сер, более низкий доход, и более высокое энергопотребление. У клиентов также есть пользовательские требования SRAM. Чтобы производители MCU предоставили все возможные размеры кэша, потребует от них слишком великого портфеля продуктов, чтобы управлять. Это привело к ограничению встроенного SRAM на ядре контроллера и кэшировал его через внешний SRAM.

Однако, Поскольку внешний SRAM занимает большое количество площади платы PCB, Использование внешнего SRAM сталкивается с проблемой миниатюризации. Из-за своей шестипозисторной архитектуры, Уменьшение размера внешнего SRAM путем переноса внешнего SRAM в меньший узел процесса введет те же проблемы, которые мужиаатрализовали встроенный SRAM.

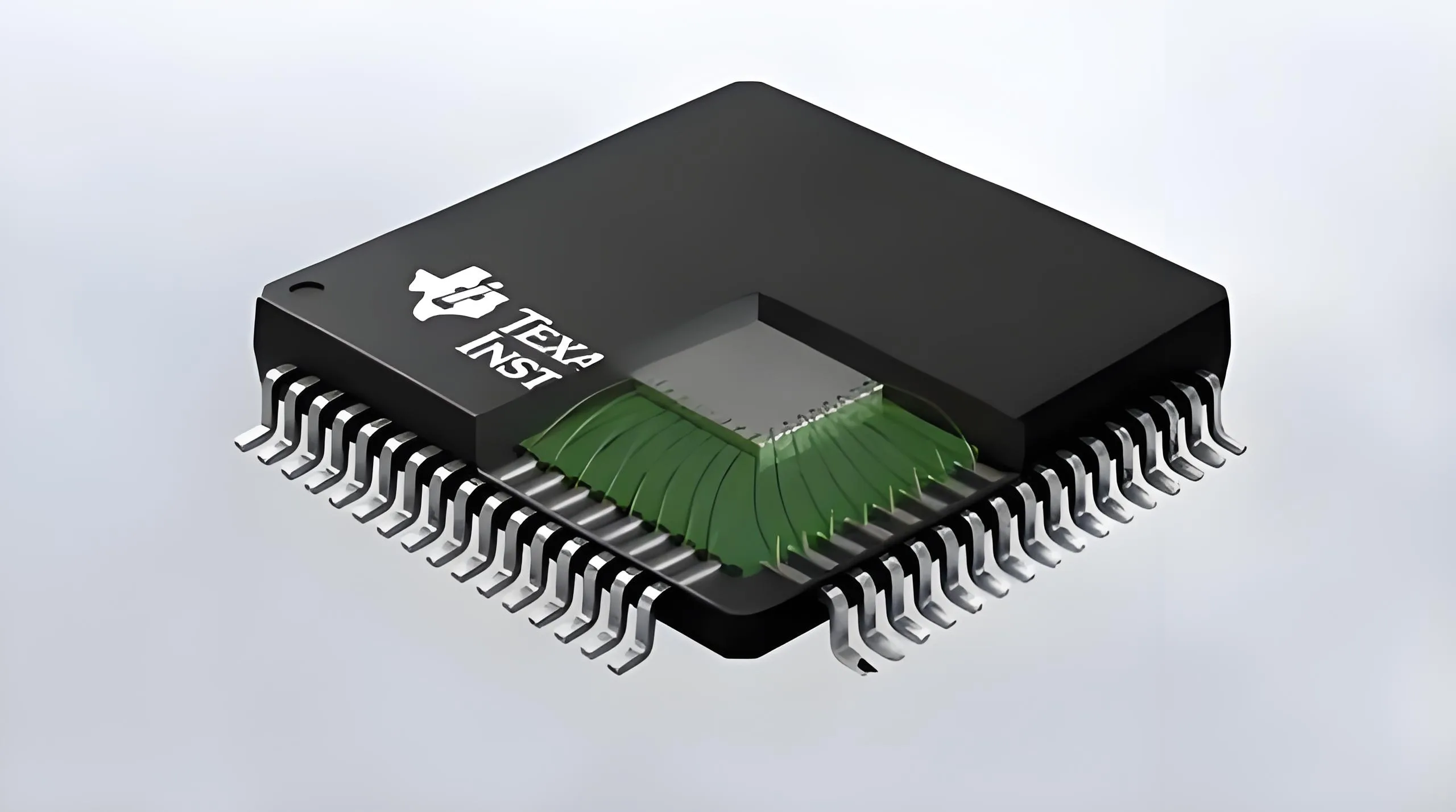

Это подводит нас к следующей альтернативе этой старой проблеме: Сокращение соотношения упаковки чипа к размеру чипа во внешнем SRAM. Обычно, упакованные чипсы SRAM во много раз превышают чип. (до 10 раз). Общее решение этой проблемы состоит в том, чтобы вообще не использовать инкапсулированные чипсы SRAM вообще. Имеет смысл взять чип SRAM (1/10 размер) а затем упаковывает его с помощью чипа MCU, используя сложную многоцветную упаковку (MCP) или технология 3D -упаковки (Также известная как упаковка SIP-системного уровня). Но этот подход требует значительных инвестиций и возможен только для крупнейших производителей. С точки зрения дизайна, Это также снижает гибкость, потому что компоненты в SIP нелегко заменить. Например, Если доступна новая технология SRAM, Мы не можем легко заменить чип SRAM в SIP. Чтобы заменить любой из голых чипов в упаковке, Весь глоток должен быть повторно. Преобразование требует реинвестирования и больше времени.

Так есть ли способ сохранить пространство на доске, исключая SRAM из MCU, не ставят MCP в беде? Возвращаясь к соотношению размера ядра к шипе, Мы видим место для значительного улучшения. Почему бы вам не проверить, есть ли упаковка, которая подходит к форме? Другими словами, Если вы не можете распаковать, Пожалуйста, уменьшите масштаб размера.

В настоящее время наиболее продвинутым подходом является сокращение размера пакета чипов с помощью WLCSP (пакет уровня чипов на уровне пластин). WLCSP относится к технологии вырезания отдельных единиц из пластины на мелкие кусочки, а затем сборку их в упаковке. Устройство по сути представляет собой чип с поднятой точечной или сферической массив. В зависимости от спецификаций, область пакета на уровне чипов 20% больше, чем у чипа. В настоящее время процесс достиг инновационного уровня, на котором производственные предприятия могут производить компоненты CSP без увеличения области чипа (с небольшим увеличением толщины, чтобы соответствовать ударам/сфере).

Числа. Пластина – на – Чип -упаковка (WLCSP) предоставляет наиболее продвинутый метод для уменьшения размера упакованного. – чип. WLCSP, показанный здесь. (Кредит: DECA Technologies/ Cypress Semiconductor)

CSP имеет некоторые преимущества перед фильмом без покрытия. Устройства CSP легче проверить, ручка, собирать, и переписать. Они также обладают повышенными свойствами теплопроводности. Когда ядро передается в более новые узлы процесса, возможно уменьшить ядро при стандартизации размера CSP. Это гарантирует, что компоненты CSP могут быть заменены новым поколением компонентов CSP без каких -либо осложнений, связанных с изменением формы.

Очевидно, Эти экономии пространства важны с точки зрения спроса на носимые устройства и портативную электронику. Например, BGA с 48 мячами, используемая в памяти IC во многих носимых устройствах сегодня имеет размер 8 ммх6 мм1 мм (48мм3). Для сравнения, Та же часть в пакете CSP измеряет 3,7 ммх .3,8 ммх.5 мм (7мм3). Другими словами, Вы можете уменьшить объем 85%. Эта экономия может быть использована для уменьшения площади и толщины печатной платы для портативных устройств. Как результат, Спрос на устройства на основе WLCSP от носимых устройств и Интернета вещей (Интернет вещей) Производители не ограничиваются SRAM, Но есть новый спрос.

ЛОГОТИП УГКПБ

ЛОГОТИП УГКПБ