Освоение контроля импеданса печатной платы: Расширенные стратегии для высокоскоростной конструкции схемы

Фигура 1: Критические следы по контролю за импедансом в проектировании многослойных печатных плат

Критическая роль контроля импеданса в современной электронике

Почему совпадение импеданса имеет значение в высокочастотных дизайнах

В высокоскоростных цифровых системах, работающих выше 1 ГГц, печатная плата Следы превращаются из простых проводников в сложные линии передачи, где характерный импеданс (Z₀.) становится первостепенным. Когда между компонентами возникают несоответствия Z₀, Сигнальные отражения могут достигать 35% инцидентной власти, вызывая искажения формы волны и ошибок времени.

Ключевые последствия плохого контроля импеданса:

- Деградация целостности сигнала: Разъединение времени 40% В интерфейсах DDR4

- ЭМИ радиационные шипы: Несоответствующие линии могут увеличить излучаемые выбросы на 15-20 дБ

- Проблемы целостности власти: Результаты возвращения

Фундаментальные концепции импеданса

Характерная формула импеданса для микрополосков:

Z₀ = frac{87}{\SQRT{e_r + 1.41}} \ln осталось(\фрака{5.98ЧАС}{0.8Вт + Т}\верно)

Где:

- ε_r = диэлектрическая постоянная (ФР4: 4.2-4.7, Роджерс 4350b: 3.48)

- H = диэлектрическая толщина (мм)

- W = ширина трассировки (мм)

- T = толщина меди (унция)

Расчет дифференциальной пары:

Z_{разница} = 2Z₀ осталось(1 - 0.48e^{-0.96S/H.}\верно)

S = пары между интервалом, H = высота диэлектрика

Пять столбов инженерии импеданса печатной платы

1. Матрица выбора материала

| Тип материала | ε_r @10 ГГц | Потеря касательной | Индекс затрат |

|---|---|---|---|

| ФР-4 | 4.5 | 0.02 | $ |

| Роджерс 4350b | 3.48 | 0.0037 | $$$ |

| Я -ра -остров | 3.45 | 0.0031 | $$$$ |

| PTFE Composite | 2.2-3.0 | 0.0009 | $$$$$ |

Стол 1: Высокочастотное сравнение ламинатов

2. Принципы архитектуры Stackup

Оптимальный 12-слойный HDI Stackup для сигналов 25 Гбит / с.:

- L1: Сигнал (0.5унция)

- L2: Земля

- L3: Сигнал (3.5Мил Диэлектрик)

- L4: Власть

- L5: Сигнал (Высокоскоростной)

- 16 -й: Земля

… Зеркальная симметричная структура

Критические параметры:

- Толерантность к толщине диэлектрика: ± 10% максимум

- Шероховатость меди: <2мкм среднеквадрат для >10ГГц

- Последовательное ламинирование для непрерывности импеданса

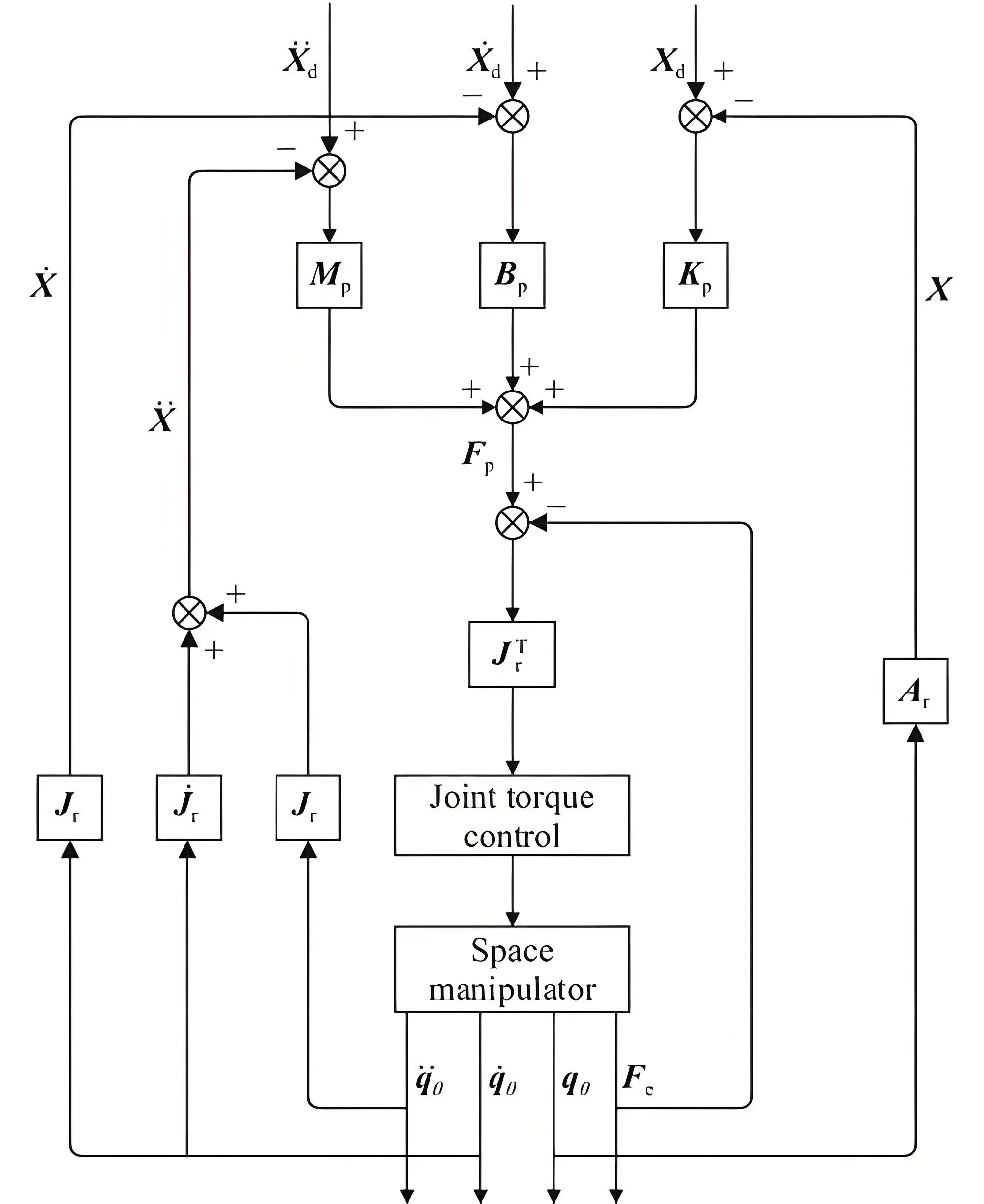

3. Расширенные методологии расчета

Трехступенчатый процесс проверки импеданса:

- Начальная оценка:

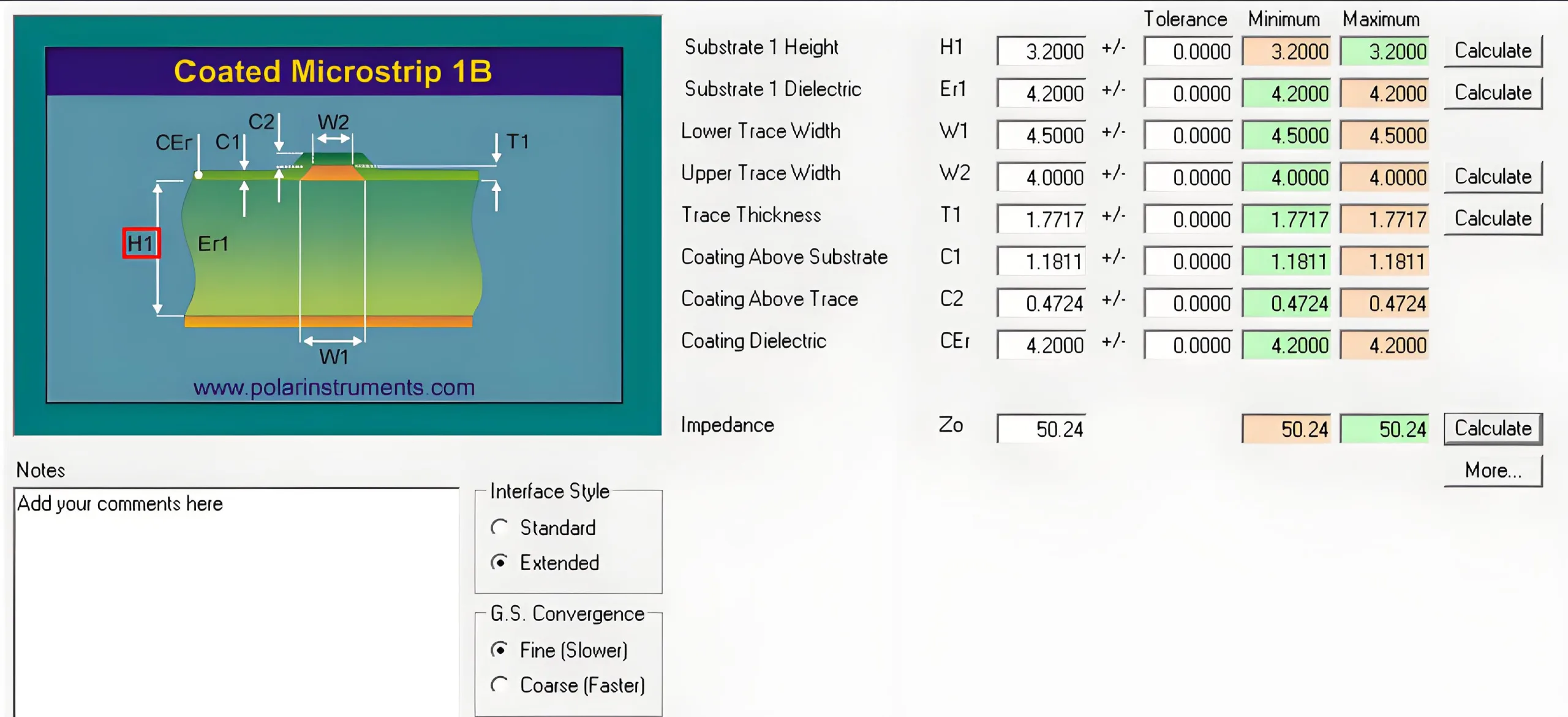

Используйте эмпирическую формулу:W PID FRAC{100ЧАС}{\SQRT{e_r}} \квадратный (\текст{50Ω Микрополос}) - Точное моделирование:

- Polar Si9000 для многослойных структур

- Rogers MWI-2017 для RF/микроволновой линии

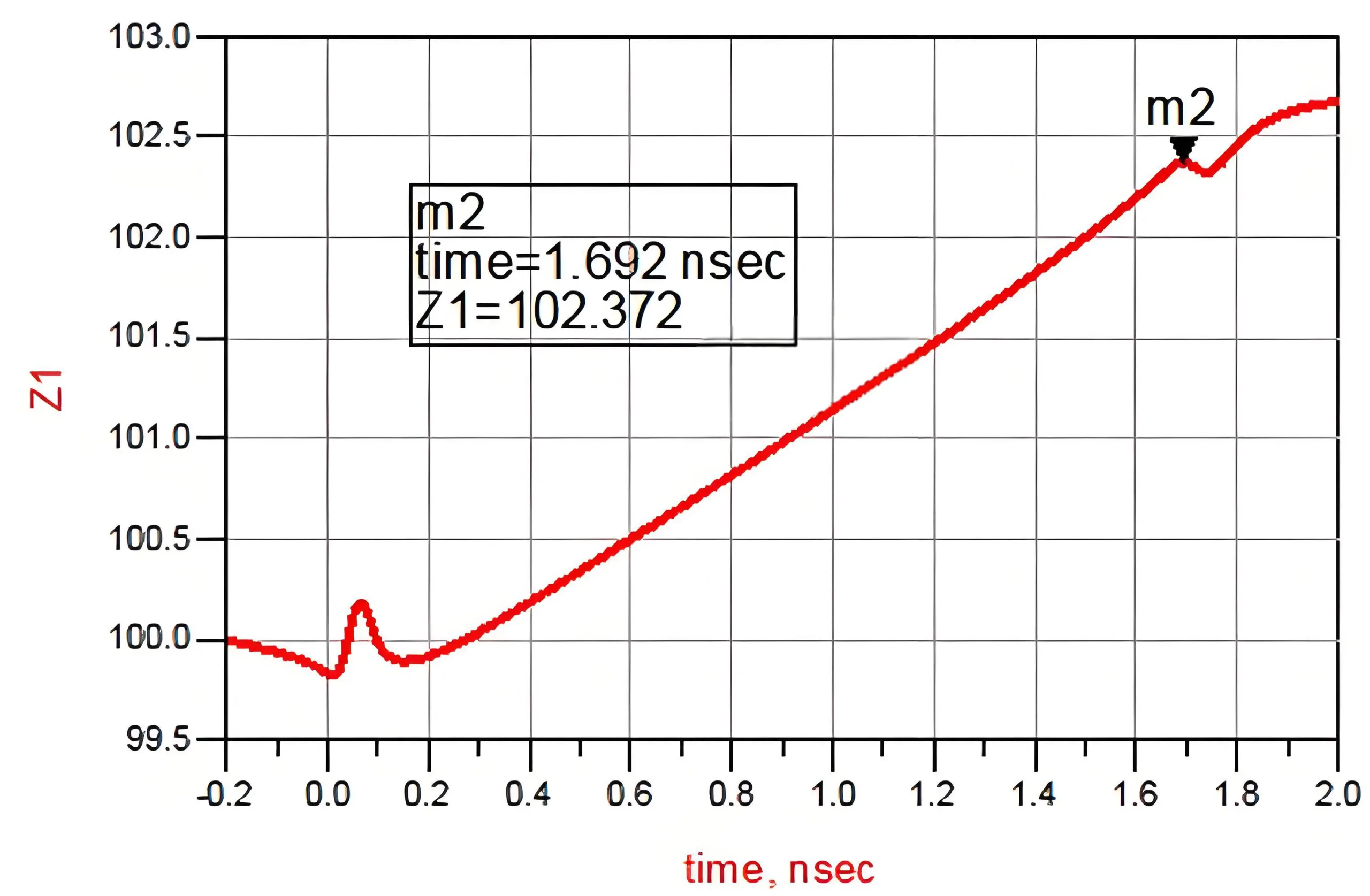

- Проверка послепроизводства:

Измерения TDR с <5% терпимость

Фигура 2: Рабочий процесс импеданса PCB

Фигура 2: Рабочий процесс импеданса PCB

4. Управление производственными процессами

Критические факторы толерантности:

| Параметр | Типичная терпимость | Воздействие на Z₀ |

|---|---|---|

| Ширина травления | ± 0,5 млн | ± 3 Ом |

| Диэлектрическая толщина | ± 10% | ± 8 Ом |

| Медный вес | 0,2 унции | ± 2 Ом |

| Soldermask | 0.3-0.5мил | ± 1,5о |

Данные из стандартов IPC-2141A

Стратегии смягчения:

- Используйте компенсированные произведения искусства (0.75× Этч -фактор)

- Реализовать автоматическую оптическую проверку (АОИ)

- Укажите купоны на контролируемый тест на импеданс

5. Экосистема передовых инструментов

Ведущие программные решения в отрасли:

- Полярные инструменты Si9000e

- 2D Полевой решатель с 47 transmission line models

- Batch processing for complex designs

- Rogers MWI-2017

- Specialized for microwave designs up to 110GHz

- Integrated material database with 50+ substrates

- Cadence Sigrity Aurora

- 3D EM simulation with <2% error margin

- DDR5/PCIe6.0 compliance checking

- Altium Impedance Profiler

- Real-time impedance visualization

- Automated stackup validation

Practical Design Guidelines for Engineers

Golden Rules for First-Time-Right Designs

- 3W Rule for Crosstalk Control:

S ≥ 3×W \quad (\текст{Where S = trace spacing})

- Length Matching Priorities:

- Differential pairs: <5mil intra-pair mismatch

- Bus signals: <100ps delay skew

- Via Optimization Techniques:

- Use 8-12mil diameter for 10Gbps signals

- Backdrilling for stub length <15% of rise time

- Termination Strategies:

Тип Приложение Power Cost Series 22Ω Source-end Low Parallel 50Ω End-point Высокий AC Capacitive DDR Memory Interfaces Medium

Future Trends in Impedance Management

Влияние новых технологий

- 5G Mmwave Проблемы:

- 28/39Полосы GHZ требуют допусков ± 1, Ом

- Лазерная абляция для контроля ширины линии 2 мкм

- Усовершенствованная интеграция упаковки:

- 3D IC с сопоставлением импеданса TSV

- Гибридный субстрат PCB-Flex Designs

- Оптимизация импеданса, управляемой ИИ:

- Нейронные сети, прогнозирующие различия в производстве

- Генеративный дизайн для решений из нескольких ограничений

Принять меры, чтобы получить цитату

УГКПБ занимает лидирующую позицию в обоих печатной плате (Печатная плата) и PCBA (Печатная плата в сборе) секторы, Сделать это лидером отрасли. UGPCB может похвастаться опытной группой разработчиков печатных плат, которая превосходит контроль над импедансом печатной платы, рейтинг в авангарде отрасли. Если у вас есть какие -либо вопросы или требования к проектированию, связанные с импедансом печатной платы, Пожалуйста, свяжитесь с нашим профессиональным техническим персоналом для технической поддержки или предпринять меры и запросите конкурентную цитату сегодня.

ЛОГОТИП УГКПБ

ЛОГОТИП УГКПБ